对具有四相逻辑的早期计算器芯片进行逆向工程

1969年,高密度MOS集成电路仍然是新事物,并且以多种方式构造逻辑电路。一种技术是"四相逻辑"它提供了十倍于标准逻辑门的速度和密度。同时使用1/10的功率。 1四相逻辑的一个显着应用是计算器.1969年,夏普(Sharp)推出了首款由高密度MOS芯片QT-8D构建的计算器,随后是世界上最小的手持式EL-8计算器。是高端产品,售价345美元(今天约为1800美元)。

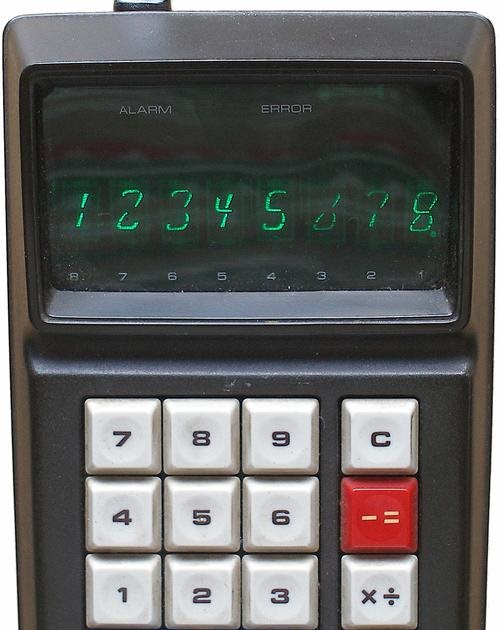

夏普EL-8计算器。请注意数字的异常8段显示。 Felix Maschek摄影,CC BY-SA 3.0 DE。

当时的集成电路密度不足以在一个芯片上实现整个计算器的功能,因此这些计算器将功能划分为五个IC。这五个芯片是由Rockwell的Autonetics部门为Sharp设计的。 1960年代中期,因此该逻辑系列是计算器芯片的自然选择。

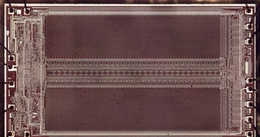

在这篇博文中,我对上图所示的键盘/显示芯片进行了逆向工程,这张照片显示了显微镜下的微小硅片,硅基板的颜色为紫色,而掺杂的导电硅为绿色,顶部的金属层为白色。在边缘附近,细的键合线将管芯连接到42个外部引脚上。该芯片包含约500个晶体管,实现100个逻辑门。 1960年代。

下图显示了计算器内部的电路板。该电路板由四个带有圆形金盖的大型集成电路所控制。这些集成电路被封装为具有交错引脚的42引脚陶瓷IC,这种布置为PCB迹线提供了更多的空间。与现代印刷电路板不同,该电路板上的迹线板是弯曲的,显示其手绘布局。

夏普EL-8计算器的电路板。时钟IC是中间的小型金属罐封装。照片来自rf先生(CC BY-SA 4.0)。

这四个芯片具有不同的功能:算术芯片,小数点芯片,小键盘/显示芯片和控制芯片。本博客文章重点介绍左上方的小键盘/显示芯片(NRD2256)。时钟芯片位于提供四相定时脉冲的小型金属罐中。系统时钟的运行频率约为60 kHz,按照微处理器标准,该速度非常慢,但对于计算器而言足够快

键盘/显示芯片的一项功能是处理按键,将数字键转换为4位串行二进制值(出乎意料的是,其他芯片处理非数字按键)。第二个主要功能是在键盘上显示数字。与大多数计算器一样,此计算器可以多路显示;它一次显示一位数字,重复的速度足够快,以使显示看起来均匀。它是通过一次激活一个显示管并激励适当的段来产生所需的数字来实现的。 2

夏普EL-8计算器的显示板。请注意顶部显示减号和错误点的特殊管。照片由John Wolff's Web Museum提供©2012。

四个主要芯片进行串行通信,将每个十进制数字作为四个BCD(二进制编码的十进制)位发送。每个通信周期由8位数字和第九个未使用的点组成,形成一个36位的``数据包''。 3基本定时来自60千赫兹时钟芯片;每个时钟周期发送一位。键盘/显示芯片产生额外的定时信号,使所有内容保持同步。首先,它将时钟除以4,生成“数字时钟”。指示每个4位数字的信号。键盘/显示芯片在显示数字之间循环,每四个时钟一位。它会向其他芯片发送信号以跟踪当前数字。因此,当键盘/显示芯片在显示屏的数字之间循环时,它将在正确的时间接收每个数字的二进制值。

下图显示了键盘/显示芯片中的功能单元。电路扫描通过八位数字驱动线D1-D8。电路反序列化小数点输入" dp"并在指定的数字处于活动状态时激活小数点段。电路将数字按键转换为四个串行位。部分仅是芯片的上半部分和下半部分之间的布线,显示了信号路由浪费了多少空间。在下半部分," 9段解码器"照亮适当的段以显示数字;此数字由"数字锁存器"序列化。 " clk÷4"电路。最后,用“键编码”将输入时钟除以四以产生数字时钟。电路将按键(0-9)转换为&digit序列化"使用的四位值。可以看出,这些功能模块不是很复杂,每个模块可能包含20个门。

计算器芯片由金属栅PMOS晶体管构建。这种晶体管在1960年代很容易制造,但很快就过时了。这些晶体管需要较大的负电压,用于计算器芯片为-25伏(为简单起见,我将信号视为低电平有效; 0V为逻辑0,而-25V为逻辑1)金属门晶体管的另一个问题因为大多数芯片被硅和金属布线占据,所以晶体管的密度很低。

下图说明了一个金属栅极PMOS晶体管,在底部掺杂了两个硅区域(绿色)以使其导电,从而形成了晶体管的源极和漏极栅极由硅区域之间的金属条形成,彼此分开从硅上通过一层薄薄的绝缘氧化物(这些层-金属,氧化物,半导体-赋予MOS晶体管名称)。可以将晶体管视为由栅极控制的源极和漏极之间的开关。因此,当栅极被拉至负电压(-25伏)时,PMOS晶体管导通,而当栅极为0伏时,PMOS晶体管截止。

下图显示了晶体管在芯片上的显示方式。栅极是由与掺杂的硅重叠的金属(垂直的绿色条)形成的。不便的是,将金属层连接到硅的触点看起来非常类似于该芯片中的晶体管-晶体管中的金属层几乎接触硅,当触点中的金属层接触硅时,可以很容易地区分触点和晶体管。如下所述,四相逻辑通常使用晶体管,其栅极和漏极都连接到同一时钟;这种连接出现在下面。通过识别晶体管,可以对电路进行逆向工程。

四相逻辑是一种用于构建逻辑门(例如NAND门)的技术。当时,构建逻辑门的标准方法称为``静态逻辑'',因为只要输入保持输出不变即可。静态逻辑的一个缺点是它需要一个很大的负载晶体管。连续使用电流,导致高功耗。

解决这些问题的方法是"动态逻辑"。代替从门提供稳定的输出,门的输出由时钟信号控制。门的值将被计算,然后由电路的电容存储,而不需要连续的电流。但是,由于动态逻辑的发展与时序有关,因此采用动态逻辑进行开发可能很棘手。 (它的另一个缺点是输出值会迅速泄漏出去,而不是像静态逻辑那样稳定。)动态逻辑仍以多米诺逻辑的形式用于现代CPU中。

四相逻辑是一种特定类型的动态逻辑,旨在简化设计过程,其时序由四个时钟信号(如下所示)控制,该时钟信号的名称为" four-phase&#34 ;. 4在计算器中,这些时钟信号以60 kHz的频率重复。

这显示了四相时钟的一个周期。四相时钟由该特定模式的四个时钟信号组成。

下图显示了如何以四相逻辑实现反相器。在第一个时钟阶段,φ1为高电平,导致电容器充电;在第二个时钟阶段,确定门的值。为0时,电容器保持其先前的值(1)。但是如果输入为1,则电容器通过较低的晶体管放电,因此输出为0,因此电路将输入反相。 5电容器在时钟周期的剩余时间内保持输出,因此门极也充当锁存器(这是四相逻辑的重要功能,简化了许多电路)。

四相逆变器的运行。门首先被预充电。在评估步骤中,栅极要么保持充电状态(如果输入为0),要么放电(如果输入为1)。

以类似的方式构建更复杂的门。对于“与非”门,多个输入晶体管串联放置。如果所有输入均为1,则电容器将放电,而输出将为0。任何1输入都会产生0.后面将会看到,可以使用串联和并联晶体管的混合来创建复杂的门。

上面描述的门仅使用两相6,为什么要使用四相逻辑?上述电路的问题在于,如果将两个门连接在一起,则在第2步中,第一个门的输出将发生变化,而第二个门正在使用值。这可能导致第二个栅极错误放电,从而产生错误的答案,解决方案是让第二个栅极等待直到第一个栅极稳定为止。具体来说,第一个栅极在时间段1和2内运行,而第二个栅极在时间段2内运行。然后在时间段3和4中将第二个门安全地连接到在时间段1和2中运行的另一个门。交替使用两种类型的门的电路将安全地运行。 7

下图显示了四相逆变器如何出现在芯片上,原理图与以前相同,但电路是垂直拉伸的,布局又高又瘦,逆变器由掺杂的硅线(绿色)组成垂直运行,与金属布线交叉。栅极由三个小晶体管实现。中间的大电容器保持输出电压。通常会建立动态逻辑以使用布线的杂散电容,但此芯片使用许多大电容器(可能是由于泄漏或时钟速度慢所致)。

在下一部分中,我将描述如何使用四相逻辑实现一些计算器IC电路。

该芯片使用移位寄存器将串行输入信号转换为并行二进制值。一个移位寄存器用于小数点位置输入,而另一个移位寄存器处理要显示的数字。移位寄存器的基本实现是每级有两个反相器的反相器。由于时钟采用四相逻辑,因此每个时钟周期将有一个位通过两个反相器(在Φ1/Φ2时一个反相器,在Φ3/Φ4时另一个反相器)这是四个优点相逻辑;标准逻辑要求每级都有一个触发器来保存位,从而使电路复杂得多。每级都有一个额外的反相器来输出不互补值。为了使两个输出保持同步,这些反相器使用特殊的时序,对Φ3进行预充电并读取在Φ1上。 7

下图显示了如何在芯片上实现小数点位置的移位寄存器,并显示了由27个晶体管实现的9个反相器。掺杂硅的每条垂直绿线是一个栅极,而白色金属布线则大部分是水平的。请注意,该电路只有九个门,占据了裸片的很大一部分。栅极紧密地并排封装时,它们非常高,因此管芯仅容纳两排栅极。晶体管的密度非常低,大部分面积被布线消耗。即使如此,四相逻辑被认为是创建门的密集方法,因为其他技术甚至更糟。(几年后,微处理器使用了一层额外的多晶硅布线,这使得信号路由变得更加容易,并极大地提高了密度。)

图中显示了晶体管和电容器的示例。底部的箭头显示了两个逆变器之间的连接之一。水平的短线连接到左侧的逆变器,形成右侧的逆变器的栅极。其他电线则较长,因为它们将逆变器连接到其他部分的电路。

该芯片使用如下所示的NAND门将每个数字按键转换为二进制编码。计算器的按钮是磁铁,闭合簧片开关。这些开关连接到右侧的输入。当按下一个键时,输入变为低电平,电路在底部产生相应的4位二进制输出。

按键编码器使用“与非”门将按键转换为二进制编码。圆圈可能是蒙版对齐标记。

每条垂直的绿线对应于一个NAND门(这些门与前面的门一样高,但是我只显示了有趣的部分)关于编码器的有趣的事情是二进制表示在晶体管模式中可见例如," 1"位输出连接到交流输入,而" 4"位输出由键4至7激活。未标记的行用于确定是否按下了任何键。

台式机QT-8D计算器使用不寻常的9段显示屏弯曲的段,而手持式EL-8使用8段显示屏(省略段i,在4处提供尾巴),它们产生弯曲的数字,而不是块状在大多数计算器中看到的7段数字。零特别不寻常:它是一半的高度。计算器不会抑制前导零,因此半高零不那么引人注目。 (例如,1234显示为oooo1234。)

QT-8D计算器中使用的9段真空荧光显示管。中间的垂直线是加热的阴极,而六角网是网格。

段解码器的作用是获取二进制值并驱动适当的段,标记为a到i。下面的电路是解码器电路中有趣的部分。位值及其补码在移位寄存器的右侧输入。大多数段均通过AND-NOR门进行解码;一个AND-NOR门由多个AND项组成,结果NOR'd在一起.AND-NOR门以四相逻辑实现为单个门,每个AND项具有单独的垂直条带。一起在顶部和底部,因此,如果任何条带被激活,则将浇口排出;结果,门的物理结构直接映射到其逻辑结构。

段f的门在图中用箭头指示。它有两个垂直条,所以有两个AND项。通过研究晶体管的连接,thisgate实现了:bit1 NOR(bit3 AND bit2),计算该表达式表明f对于数字4、5、8和9处于活动状态。查看显示屏,您可以验证这些数字是否有效使用段f的相似表达式用于生成其他段。例如,段h具有四个AND项。

段i由一个或非门激活,该门有两个平行的垂直段,中间有三个晶体管,如果任何一个晶体管被激活,它将连接这些段并使门放电,从而提供或非作用。因为它们需要两倍于NAND门的宽度。段i为NOR(bit0,bit2,bit1),所以仅对数字4激活;此段在显示的4上提供了一条短尾巴。

该芯片的任务之一是显示小数点,这比您预期的要复杂。小数点被编码为4位值,并串行传输到芯片。三位表示小数点的位置(0到7),而第四位启用或禁用小数点。移位寄存器(如前所述)将串行位转换为4位值。用于确定有效数字何时与指定的小数点位置匹配。那时,小数点段被激活,导致正确的小数点点亮。

该电路以四相逻辑实现为单个门,该门可以看作是8位至1位多路复用器,可根据位值选择八位(D)线之一。该门还包括一个锁存器注意,如果数字时钟为0,则底部的“与”门将循环输出值(通过一个未显示的反相器),并保持该值。当数字时钟为1时(即已读入一个数字),将从多路复用器树中读取新值。在上面的硅结构中可见分支树结构。

我不会详细描述芯片上的其余电路,它们是使用类似的技术实现的,特别是移位寄存器。按键是通过一个由AND-NOR门构建的锁存器和移位寄存器转换为串行数据的数字扫描电路也是锁存器和移位寄存器,其门开始为1值。该移位寄存器是由字节数字时钟触发的,因此每4个周期移位一次。将时钟除以4的电路是一个移位寄存器,用于计数4个周期。

尽管夏普设法将计算器电路装配到五块芯片上,但很快就被单芯片计算器所掩盖。几年后,计算器从手持式但笨拙的夏普EL-8缩小到信用卡大小,计算器市场利润丰厚。持续很短的时间,直到"计算器大战导致计算器价格从几百美元降至几美元。数百家计算器制造商中的大多数都退出了市场,而德州仪器,惠普,夏普和卡西欧则是主要制造商。

至于四相逻辑,其成功在1970年代达到顶峰。最著名的是,四相系统公司(Four-Phase Systems)于1971年使用四相逻辑创建了24位台式计算机,而摩托罗拉(Motorola)于1982年收购了该公司。不过,1970年代的微处理器使用的是静态NMOS逻辑,而不是四相逻辑。我无法找到为什么四相逻辑没有得到更广泛使用的解释。我的怀疑是,1970年代初期改进的半导体技术降低了四相逻辑的优势,特别是耗尽型NMOS逻辑的引入。

我计划分析剩余的三个计算器芯片,因此在Twitter上关注我@kenshirriff进行更新。我也有RSS提要。感谢FrançoisGueissaz辛辛苦苦地获得了计算器IC,将它们拆盖并为我提供照片和其他信息。

MOS电路和四相逻辑的早期支持者Lee Boysel在一次演讲中讨论了四相逻辑的优点。他创建了公司Four-Phase Systems,该公司使用四相逻辑构建了功能强大的台式计算机,有关MOS历史的有趣视频也在这里。 ↩

计算器显示器使用真空荧光显示(VFD)灯管,该灯管是代替Nixie灯管的低成本替代产品,以避免向Burroughs支付专利使用费。 有10个阴极,每个阴极的形状像一个数字,向阴极施加170伏特的电压使数字随着霓虹灯发光。 多段式VFD由Noritake Itron Corp.于1967年发明。 ......