对经典的MK4116 16K位DRAM芯片进行逆向工程

早在20世纪70年代末,最流行的存储芯片就是Mostek&39;MK4116,当时的存储容量高达16千位。它为Apple II、TRS-80、ZX Spectrum、Commodore PET、IBM PC和Xerox Alto等计算机以及视频游戏(如防御者和导弹指挥部)提供存储。为了了解芯片是如何实现的,我打开了一个芯片,并对其进行了反向工程。我本以为电路会类似于那个时代的其他芯片,使用标准的NMOS门,但它比我想象的要复杂得多。1%2。

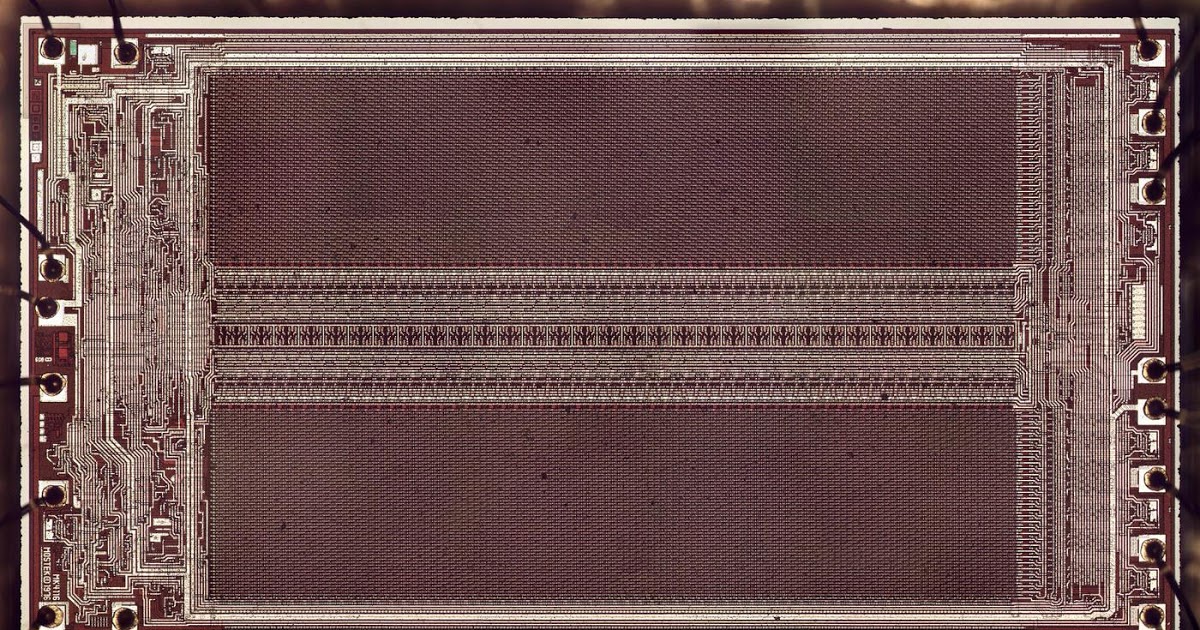

我根据多张显微镜图像制作了下面的芯片照片。白线是芯片顶部的金属布线,而下面的硅显示为暗红色。两个大的矩形区域是16,384个存储单元,排列成一个128×128的矩阵,一分为二。在两个存储阵列之间是放大器和选择电路。控制和接口电路在左右两边,通过微小的焊线连接到外部引脚。

在动态RAM中,每个位都存储在电容中,位的值0或1由电容器上的电压表示。3动态RAM的优点是每个存储单元非常小,因此可以在一个芯片上存储大量数据。4动态RAM的缺点是电容器上的电荷在几毫秒后就会泄漏。为了避免丢失数据,动态RAM必须不断刷新:从电容器读取位,放大,然后写回电容器。对于MK4116,所有数据必须每隔两毫秒刷新一次。

下图显示了16,384个存储单元中的4个。每个存储单元都有一个电容器,以及一个将电容器连接到相关位线的晶体管。为了读取或写入数据,需要给行选择线通电,使该行中的晶体管导通。行的电容器连接到位线,允许访问该行中的位。

Mostek的关键创新之一是多路复用地址引脚。6早期的内存芯片对每个地址位使用单独的管脚;随着内存大小的增加,地址管脚的数量也随之增加。例如,这迫使英特尔的4096位内存芯片使用更大、更昂贵的22管脚封装。5Mostek将每个地址引脚使用两次,将地址引脚数量减半,第一次是针对行地址,然后是列地址。这一方法成为行业标准,使存储芯片可以放入廉价的16针封装中。

在外部,该芯片存储16,384个不同地址的单个位。(通常,这些芯片中的8个被并行使用来存储字节。)然而,在内部,芯片被实现为128×128个存储单元的矩阵。行地址选择128个单元7的行,然后列地址选择这128个单元中的一个进行读或写。同时,通过放大信号并将它们存储回电容器来刷新整行128个单元。

4116的模具上标有密钥块。大部分存储单元区都被切割掉了。

上面的芯片图像标有主要功能块。芯片的16个引脚被标记在周边,10个引脚包括7个地址引脚(A0-A6)。行地址选通引脚(RAS)用于指示行地址已准备好,而列地址选通引脚(CAS)用于指示列地址已准备好。两个存储器阵列位于中央;I';为了保持图的紧凑,我们去掉了大部分单元。列选择电路和读出放大器位于两个存储器阵列之间。在右边,行译码电路根据地址引脚选择行,而列地址电路缓冲列选择电路的地址。在左边,时钟电路产生芯片的定时脉冲,由RAS、CAS和写入引脚触发。最后,数据输出和数据在引脚中提供访问

DRAM芯片的关键是存储器存储单元,设计得尽可能紧凑。下面这张高度放大的照片显示了一些存储单元,它们密集地堆积在一起。很难想象是什么东西。这是因为芯片是由多层构成的。最底层是灰色的硅晶片。在硅片的顶部是两层多晶硅,这是一种用于晶体管栅极、电容器和布线的特殊类型的淀积硅。芯片的顶层是金属布线,在这张照片中去掉了金属布线。照片显示了硅片中的三条位线,两边都连接着灯泡状的存储单元。存储单元上方的垂直多晶硅条带(Poly1)实现了电容器:硅形成了较低的电容层。而多晶硅形成上平板。第二层多晶硅(多晶硅2)设置在对角区域以实现选择晶体管,其中多晶硅1层中的方形凹槽允许多晶硅2层接近硅。

下面的截面图显示了存储单元的三维分层结构。底部是硅(棕色);位线(深棕色)是由掺杂的硅制成的。硅的旁边是由绝缘二氧化硅(灰色)隔开的两层多晶硅层(红色)和金属层(紫色)。在最左边,多晶硅1层和下面的硅形成电容。在电容器和位线之间,多晶硅2层形成晶体管的栅极。在左边,多晶硅2层连接到字线的金属,使晶体管导通,将电容器连接到位线。

存储单元的横截面结构。基于16K-新一代动态RAM。

下图说明了如何在存储矩阵中寻址比特。这种排列有些令人困惑,因为单元列像拉链一样错开和互锁。行选择线连接到对角线Poly2区域的中心,因此每个区域控制相邻位线上的两个晶体管。(例如,在左上角,连接到行选择0的多晶区形成晶体管0A和0B。)结果是,每条行选择线激活128个单元,交错排列中的每条位线对应一个单元。(例如,在左上角,连接到行选择0的多晶区形成晶体管0A和0B。)结果是,每条行选择线激活128个单元,每个单元对应一个交错排列的位线。

矩阵中位的排列。根据其对应的行线和位线来标记晶体管。

MK4116存储芯片的一个主要特点是,它在空闲时几乎不耗电。虽然它在激活时消耗462毫瓦,但在待机模式下只消耗20毫瓦。虽然低功耗电路是用现代CMOS技术直接构建的,但4116使用早期的NMOS晶体管。大多数NMOS集成电路用负载晶体管构建逻辑门,这是一种简单的技术,缺点是浪费功率。相反,MK4116存储芯片使用的是早期的NMOS晶体管。MK4116存储芯片使用的是负载晶体管,这是一种简单的技术,但它的缺点是浪费功率。MK4116的存储芯片在待机模式下只消耗20毫瓦的功率。虽然低功耗电路很容易用现代CMOS技术建造,但4116使用的是早期的NMOS晶体管。

典型的动态逻辑门(下图)分两个阶段运行。在第一阶段,时钟信号打开上三极管,将输出预充电到+12伏,即状态。然后,上三极管关闭,但由于导线的电容,输出保持高。在第二阶段,下三极管可以拉低输出。特别是,如果输入为1,相应的三极管打开并拉低输出,因此电路实现了或非门。不消耗任何静态电源,只需很小的电流就可以在切换时给导线电容充电。(输入必须仔细计时,以免与预充电时钟重叠。)动态电路的使用使4116比不使用动态电路要复杂得多,因为栅极是由时钟信号控制的,而时钟信号需要产生。

在第一步中,32个5输入NOR门解码地址位A0到A4。这些NOR门在下面所示的紧凑电路中实现。每个NOR门采用不同的非反相和反相地址位的组合,并且匹配特定的5位地址。这些NOR门使用动态逻辑,首先拉高,然后放电到地,除了。基于A5和A6,结果是128条行选择线中的一条被激活,打开矩阵中该行的晶体管。

NOR门是在几个紧凑的模块中实现的;下面显示了一个由三个NOR门组成的块。每个NOR门都是一条掺杂硅的水平条带,上面和下面都有地。每个NOR门都有晶体管(粉红色条)交替地连接到它上面和下面。如果连接的地址线是高的,晶体管将NOR门拉低。左边的预充电晶体管将NOR门拉到+12伏,而输出控制晶体管控制解码输出到电路其余部分的流动。

行解码器中有三个或非门。垂直的黄色条带表示金属布线,在这张照片中去掉了。

位于晶体管栅极末端的小的绿色斑点(粉色条纹)是晶体管栅极和地址线之间的连接(通孔)。地址线被表示为垂直的黄色条纹(因为金属层被移除)。请注意,每个晶体管栅极在右边有一条地址线,而反转的地址线在左边;因此,Thenor门都具有相同的基本布局,但是触点被改变以匹配特定的地址。例如,上面的NOR门具有连接到A0、A2、。

读出放大器是存储芯片设计中最具挑战性的部分之一。读出放大器的工作是从电容器获取微小电压,并将其放大为二进制0或1。挑战在于,即使电容器中存储了12伏的电压,来自电容器的信号也非常小,只有100毫伏左右。(因为位线比微小的存储单元电容器大得多,所以电容器产生的电压摆动非常小。)12读出放大器的准确工作至关重要,即使在。因为任何错误都会破坏数据。由于有128个读出放大器,读出放大器电路也必须紧凑和低功耗。

128个读出放大器位于芯片的中间,在上部和下部存储器阵列之间。

如上所述,芯片的128个读出放大器(每列一个)位于两个存储器阵列之间。在读取过程中,一行中的128个值被并行访问,并被读出放大器放大。然后,这128个值被写回以刷新电容中的值。对于写操作,其中一个位在被写回之前被更新为新值。

每个读出放大器(上图)都是一个非常简单的电路。它接受两个输入并对它们进行比较,将较低的一个拉到0。它是由两个交叉耦合的晶体管组成的,每个晶体管都试图拉低另一个晶体管。无论哪个晶体管一开始的电压较高,都会迫使另一个晶体管降低电压。14读出放大器对非常小的电压差很敏感,使其能够区分存储单元中的小信号。

将读出放大器放置在两个存储阵列之间并不是任意的,而是它们运行的关键:这是1972年引入的分割位线架构。其想法是,读出放大器的一个输入是来自所需存储单元的电压,而另一个输入是来自相反存储阵列中的虚拟单元的阈值电压。虚拟单元的构造和预充电与真实存储单元一样,只是电容器的大小是一半,所以它们提供了中间的电压。3如果来自实际存储单元的电压较低,则读出放大器输出0,如果较高,则输出1。

虚拟单元提供阈值电压,用于确定位是0还是1。虚拟单元位于存储器阵列的顶部和底部。它们位于与真实存储单元相同的位线上。

虚拟单元方法的优点在于,在操作期间制造差异或波动将(希望)同等地影响真实单元和虚拟单元,因此来自虚拟单元的电压将保持在正确的电平以区分0和1。地址位A0控制阵列的哪一半向位线提供真实数据,以及哪一半连接虚拟单元。虚拟单元方法的优点在于,在操作期间制造差异或波动将(希望)同等地影响真实单元和虚拟单元,因此来自虚拟单元的电压将保持在正确的电平,以区分0和1。地址位A0控制阵列的哪一半向位线提供真实数据,以及哪一半连接虚拟单元。地址位A0控制阵列的哪一半向位线提供真实数据,以及哪一半连接虚拟单元。地址位A0控制阵列的哪一半向位线提供真实数据,以及哪一半连接虚拟单元。

列选择电路的目的是从128位行中选择一列;每一列选择电路的宽度是存储单元的两倍,所以它们只解码64列中的一列。结果是一次选择两个位,而别处的电路选择两个位中的一个。与行选择电路一样,列选择电路由多个或非门实现,每个或非门匹配一个地址。对于列选择地址位A0到A5,选择64条线中的一条,一次选择两列。这两条位线连接在一起。对于行选择电路,列选择电路由多个或非门实现,每个或非门匹配一个地址。对于列选择地址位A0到A5,选择64条线中的一条,一次选择两列。这两条位线被连接。列选择电路实际上选择了四条位线。)与行选择电路一样,使用由各种定时信号控制的动态逻辑。注意,每个NOR门在物理上被分成两个部分,读出放大器在中间。

下面的示意图显示了列解码器如何与读出放大器一起工作。该图显示了两条位线以及列解码器和读出电路的上半部分;它被镜像到较低的阵列。在顶部,读出预充电电路将所有位线拉高。在底部,读出放大器如上所述地放大和刷新信号。列解码器匹配特定的6位地址,因此64个解码器中的一个将激活相关的读出选择电路,将芯片的I/O电路连接到四条位线(两条)。列解码器与特定的6位地址相匹配,因此64个解码器中的一个将激活相关的感测选择电路,将芯片的I/O电路连接到四条位线(两条。

在这一点上,已经选择了四条位线供使用,并且它们的信号被传递到输入/输出电路;列选择电路只解码64位中的1位,而有128列,阵列的每一半都有独立的位线。列地址位A6提供两列之间的最终选择。所选位被送到数据输出管脚进行读取。对于写入,数据输入管脚上的值通过适当的导线送回以覆盖读出放大器中的值。该电路由动态逻辑和锁存器实现,并由各种时序信号控制。在许多情况下,数据输入管脚上的值被送回数据输出管脚,以覆盖读出放大器中的值。该电路使用动态逻辑和锁存器来实现,并受各种时序信号的控制。行地址位A0区分矩阵的哪一半是活动的,哪一半是提供伪数据的)。(注意,行地址位A0已经用于选择特定行,但是电路具有";(丢失了其中真实行和虚拟行的跟踪,因此它必须重新进行选择。)?

芯片在内存操作中的各个步骤需要许多计时信号。与CPU不同,内存芯片不使用外部时钟,而是在内部生成自己的计时信号。下图说明了时钟生成器,使用缓冲器在每次连续的时钟输出之间创建延迟。第一组计时信号由行存取选通脉冲(RAS)触发,表示计算机已将行地址放在地址引脚上。下一组计时信号由列存取选通脉冲(CAS)触发,指示。其他定时信号由写入引脚触发。

实际的时钟电路比图中显示的要复杂得多,由多个链上的几十个晶体管组成,以复杂的方式反馈以整形脉冲。(此外,使用动态逻辑要求每个缓冲器既有一个将其拉高的输入端,也有一个将其拉低的输入端,这几乎形成了一个圆形问题)。这些门大多由大晶体管组成,如下所示,以提供足够的电流来驱动电路,并充分增加栅极延迟。时钟电路还使用许多电容器,很可能是Boo型电容器。这些门主要由大晶体管组成,如下所示,以提供足够的电流来驱动电路,并充分增加栅极延迟。时钟电路还使用许多电容器,可能是Boo。我不打算详细描述这些钟,因为它是一个复杂的乱七八糟的东西。

该芯片的地址管脚和数据输入管脚使用了复杂得令人惊讶的电路。Mostek早期的存储芯片由于INP上的噪声容限而出现了问题

下图显示了产生1.5V基准电压的阈值产生电路。它使用许多微小的晶体管串联来产生电压电平。概念上,它类似于电源和地之间的电阻分配器来产生输出电压。但是,电阻器既耗电又难于在集成电路中构建,所以使用晶体管来代替。由于这个电路总是有效的,所以设计者需要最小化它的电流;这是通过串联许多晶体管来实现的。

用于地址引脚的基准电压源。(例如,×18表示串联18个晶体管。)。

输入引脚上的电压和阈值电压被送入差动放大器/比较器,概念上类似于读出放大器。每一端都试图拉低另一端,结果是胜方为1,输方为0。因此,输入被转换为二进制值。比较器的结果存储在锁存器中。多个定时信号选通输入信号,对电路预充电,并控制锁存器。

数据输入电路:引脚、锁存电路和基准电压源。该电路位于芯片的左下角。

上图显示了数据输入引脚的输入电路。引脚焊线旁边是阈值电路和锁存;这两个电容器是金属的大矩形。下一个是电压基准电路;数据输入基准电压源类似于上面描述的地址基准电压源。(为了这张照片,我让金属层开着;下面的多晶硅和硅被氧化层遮挡住了。)(为了拍摄这张照片,我让金属层开着;下面的多晶硅和硅片被氧化层遮住了。)(为了拍摄这张照片,我让金属层开着;下面的多晶硅和硅被氧化层遮住了。)。

这个存储芯片比我预想的要复杂得多。我之前研究了一个简单的Intel存储芯片,所以我认为这个DRAM会更大,但不会太复杂。相反,MK4116拥有复杂的电路,有超过1000个晶体管控制它,此外还有16384个用于存储单元的晶体管和大约1500个用于列选择和读出放大器的晶体管。复杂性的一个原因是设计需要优化多个轴:密度、速度和功率效率。16个。

下表显示,每一代DRAM芯片都需要实质性的技术变革和新的发展。存储器设计者不能坐等摩尔定律来增加存储器容量;他们必须不断开发新技术,因为DRAM存储单元基本上是相似的。幸运的是,DRAM设计者继续解决存储器扩展问题;16G的DRAM最近投入生产,比16千字节的MRAM高出100万倍,令人惊叹。

.