AMD三元符ZEN 3 CPU缓存使用3D堆叠技术

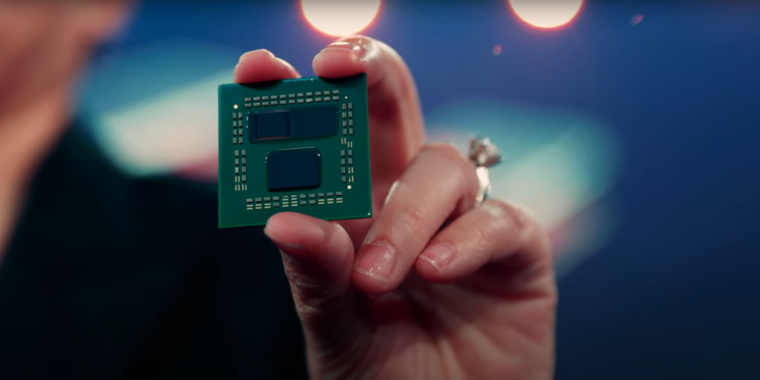

昨天在Computex 2021,AMD首席执行官Lisa Su展示了公司'下一个大型性能播放3D堆叠的小芯片,允许公司在其旗舰Zen 3 CPU上三倍的L3缓存量。

该技术只是它听起来像 - 一层SRAM缓存层坐在CPU本身的复杂核心模具(CCD)上。当前ZEN 3架构每8个核心小芯片32MIB为L3高速缓存集成为12-或16核小芯片,如Ryzen 9 5900x或5950x。新技术在每个小芯片和#39; S CCD的顶部添加了另外的64MIB L3缓存,与通过硅通孔(TSV)粘合。

附加的64MIB L3高速缓存层不会延长CCD的宽度,从而需要结构硅来平衡来自CPU冷却系统的压力。 Compute和Cache Dies在新设计中都会变薄,允许它与电流Ryzen 5000处理器共享基板和散热器技术。

RYZEN 5000上的L3缓存T3缓存允许在某些工作负载下的性能增益 - 特别是归档压缩/解压缩和游戏 - 类似于通过整个新的CPU世代看到的游戏。 AMD通过5战争的齿轮演示了性能隆起。与未指定的GPU配对,并以4 GHz固定时钟速度,电流模型5900x系统实现了184个FPS-虽然三维缓存原型管理206 FPS,但增益大约为12%。

AMD声称平均增加了15%的博彩表现与新技术,从怪物亨特联盟的11%的低点范围为4%,为怪物亨特的25%:世界。这种性能改进既不需要较小的过程节点也不增加时钟速度 - 这在时钟速度大大击中墙壁的时期,以及处理节点收缩的物理学结束似乎也在地平线上。

Anandtech' S Ian Cherress指出,AMD' S新的3D小芯片堆叠过程显然是TSMC' S Soic Chip-on-Wefer Technology行动。虽然AMD至少是如此远的自身,但TSMC在动作中展示了一个完整的12层。这里的问题是热添加RAM是一种近乎理想的技术,因为额外的硅并不是诸如额外的热量的方式产生了很多。 CPU上的CPU堆叠将更为问题。

AMD指出,重新设计的5900x将于今年晚些时候在禅宗4'在2022年之前的计划发布。目前,AMD专注于&#34的新技术;高端Ryzen"仅限CPU仅由EPYC制成,添加缓存所需的额外硅使其可能是预算处理器的最不稳定,给出了当前的材料短缺。