我们可以打破硅制造的2nm壁垒吗?

芯片制造商在最新的工艺节点上继续利用晶体管技术取得进步,但是这些结构中的互连一直在努力保持同步。

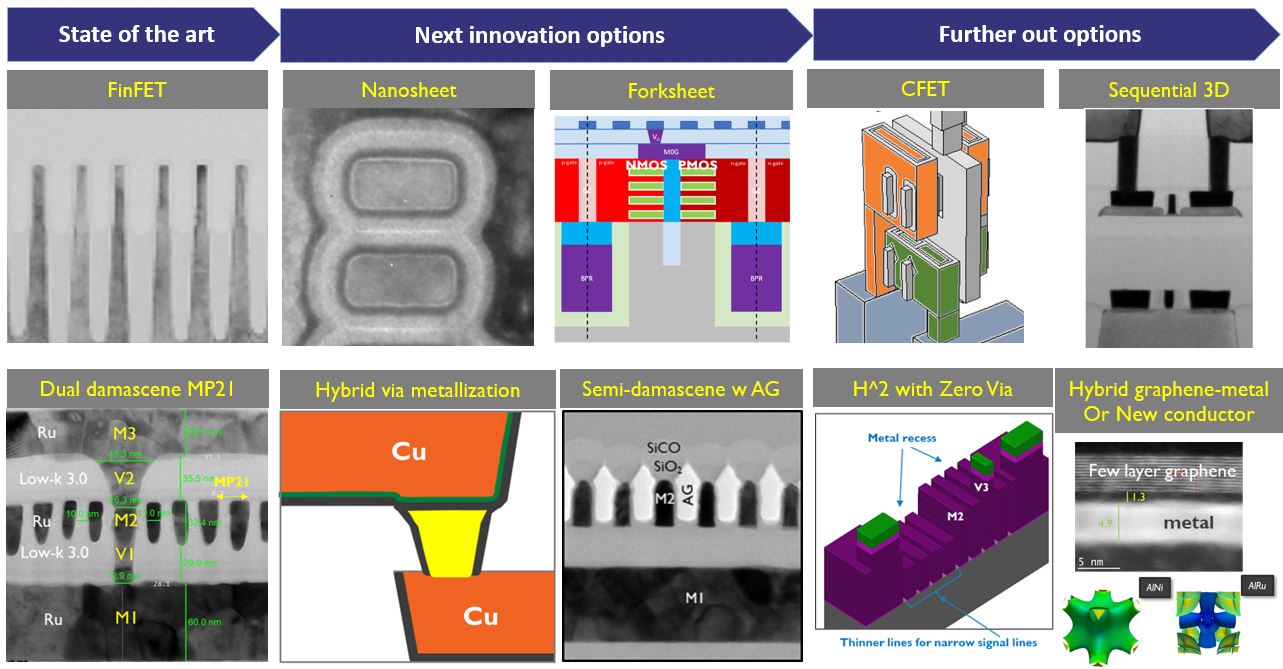

芯片行业正在研究几种技术来解决互连瓶颈,但是其中许多解决方案仍在研发中,可能不会出现一段时间-可能要到2纳米才会出现,预计将在2023/2024的某个时候推出。此外,解决方案需要使用不同材料的新型且昂贵的工艺。

在此之前,业界将继续处理先进芯片中的几个问题,这些芯片由三部分组成-晶体管,触点和互连。该晶体管位于该结构的底部,并用作开关。互连位于晶体管的顶部,由微小的铜布线方案组成,该布线方案将电信号从一个晶体管传输到另一个晶体管。当今的高级芯片由10到15层组成,每层都包含复杂的铜布线方案,并使用微小的铜过孔进行连接。

另外,晶体管结构和互连通过称为中线(MOL)的层连接。 MOL层由一系列微小的接触结构组成。

不到十年前,高级晶体管的问题开始堆积在20nm和16nm / 14nm处,那时晶体管中的铜互连变得更加紧凑,从而导致芯片中不必要的电阻电容(RC)延迟。简而言之,使电流流过细电线变得更加困难。随着时间的流逝,芯片制造商已经能够将晶体管和互连缩小到最新的节点,即7nm / 5nm。但是在每个节点上,复杂的互连方案在芯片延迟中所占的比例更大。

“随着晶体管尺寸的缩小,连接它们的金属线在多层互连堆栈的整个高层架构中也必须如此,” Lam Research大学项目主管Nerissa Draeger解释说。 “随着下一代的发展,这些局部互连变得越来越狭窄,越来越近,以至于现有的铜互连面临着进一步扩展的巨大挑战。例如,进一步减小线宽或线高将大大增加线的电阻。”

这些问题中的许多问题都可以追溯到铜互连的制造方式。为此,芯片制造商在工厂中利用了所谓的铜双镶嵌工艺。由IBM在1990年代后期开发的芯片制造商在将近25年前开始在220nm / 180nm开始使用双镶嵌工艺,并从那时起扩展了该技术。

芯片制造商将该技术推向更先进的节点,并计划将其扩展到3nm。但是,在3nm以上,RC延迟问题可能会变得更加棘手,因此业界可能需要一种新的解决方案。

找到下一代互连技术至关重要。互连与晶体管齐头并进,它们对于芯片缩放至关重要。但是,如果业界无法开发出超过2nm的下一代,具有成本效益的互连方案,那么我们今天所知道的芯片缩放可能会停滞不前。

当前在研发中的是各种新的2nm及以上互连技术。他们之中:

混合金属化或预填充。这将不同的镶嵌工艺与新材料结合在一起,以实现更小的互连,并且延迟更少。

Supervias,石墨烯互连和其他技术。随着业界不断寻找铜的替代金属,这些都在研发中。

每种提出的研发技术都面临挑战。因此,该行业在避险,并开发替代方法来开发新的系统级设计。先进的封装是这些方法之一,并且无论缩放如何发生,它都有望继续受到关注。

从铝到铜在芯片制造过程中,晶体管是在晶圆厂的晶圆上制造的。该过程在工厂的前端(FEOL)中进行。然后,在称为后端后端(BEOL)的单独fab设施中形成互连层和MOL层。

直到1990年代,芯片都集成了基于铝材料的互连。但是,当1990年代后期前沿芯片接近250nm时,铝无法承受更高的设备电流密度。

因此,从1990年代末的220nm / 180nm开始,芯片制造商从铝迁移到了铜。据IBM称,铜互连线的导电电阻比铝低40%,这有助于提高芯片的性能。

1997年,IBM宣布了世界上第一个基于220nm技术的铜互连工艺。这种被称为双镶嵌的工艺成为在芯片中制造铜互连的标准方法,并且至今仍在使用。

最初,此过程使芯片具有六层互连。当时,据WikiChip称,180nm器件的金属间距为440nm至500nm。相比之下,在5nm节点处,芯片由10至15层互连组成,金属间距为36nm。根据TEL,金属间距是指互连线之间的最小中心距。

图2:双大马士革的制造过程; (a)通过构图; (b)通孔和沟槽图案; (c)阻挡层沉积和铜种子沉积; (d)电镀铜并通过化学机械抛光去除多余的铜; (e)覆盖层沉积。资料来源:维也纳工业大学/微电子研究所

在双镶嵌工艺中,首先将低k介电材料沉积在设备的表面上。基于碳掺杂的氧化物材料,低k膜用于将器件的一部分与另一部分绝缘。

下一步是在介电材料中构图微小的通孔和沟槽。每个节点上的通孔/沟槽变得越来越小。因此,在当今的先进芯片中,芯片制造商正在使用极端紫外光刻(EUV)来对通孔进行图案化。

在未来的节点上,通孔将需要具有多种图案的EUV。布鲁尔科学公司的高级技术人员道格·格雷罗说:“ EUV多重图案化的挑战与ArFi(193nm浸没)实施过程中遇到的挑战非常相似。” “如果使用ArFi或EUV,则机器对机器的覆盖将变得至关重要。从材料的角度来看,多次构图总是包括平面化层的结合。平面化材料也称为间隙填充材料。它们必须以高纵横比填充并平坦化非常狭窄的沟槽。”

在该步骤之后,蚀刻构图的结构,形成通孔和沟槽。然后,使用物理气相沉积(PVD),将基于氮化钽(TaN)的薄阻隔材料沉积在沟槽内。然后,将钽(Ta)衬里材料沉积在TaN势垒上方。最后,使用电化学沉积(ECD)将通孔/沟槽结构填充铜。该过程在每一层重复多次,从而形成铜布线方案。

该工艺一直有效,直到20nm为止,那时互连中的铜电阻率呈指数增长,从而导致芯片延迟。因此,从22nm和/或16nm / 14nm开始,芯片制造商开始进行一些重大更改。在互连方面,许多人用钴代替了Ta作为衬里,这有助于降低互连中的电阻。

同样在这些节点上,芯片制造商也从传统的平面晶体管转向了下一代finFET,后者以较低的功率提供了更高的性能。

然后,在10nm处,英特尔又采取了降低芯片电阻的措施。英特尔的10纳米工艺具有13个金属层。英特尔的前两个本地互连层分别称为金属0(M0)和金属1(M1),其中钴是导电金属,而不是铜。其余层使用传统的铜金属。

其他芯片制造商在M0和M1处停留在铜上。但是,在10nm / 7nm的情况下,所有芯片制造商都将钨材料转移到了钴材料中以用于MOL中的微小触点,这也降低了线路电阻。

如今,领先的芯片制造商已将finFET和铜互连扩展到5nm。可以肯定的是,在高级节点上对芯片有需求,从而可以实现新的更快的系统。

“毫无疑问,即使对于非技术市场,能够以比现在快10倍的速度进行计算将具有商业上的实用性和竞争优势。 D2S首席执行官Aki Fujimura表示,对更高计算能力的需求几乎没有尽头。

不过,地平线上仍有一些令人不安的迹象。缩小晶体管的好处在每个节点上都在减少,RC延迟问题仍然存在问题。

IBM高级BEOL互连技术研究高级经理Griselda Bonilla表示:“在7nm和/或5nm铸造节点,铜互连将可能由氮化钽阻挡层和钴作为衬里。”随着尺寸的缩小,线路电阻不成比例地增加,占总延迟的比例更高。电阻增加受多种因素驱动,包括减小的导体横截面,由于未成比例的高电阻率势垒和衬里层而导致的铜体积分数进一步降低,以及由于在表面和晶界处的有损电子散射而导致的电阻增加。 ”

迈向3纳米及更高制程但这并没有阻止行业前进到下一个节点。如今,领先的代工厂正在研发5nm,3nm / 2nm甚至更高的产品。

三星计划在3nm工艺上采用下一代晶体管,即全能栅极FET。台积电计划将finFET扩展到3nm,但将转向2nm的全栅。

当鳍片宽度达到5nm(等于3nm节点)时,FinFET接近其实际极限。环栅式FET具有比finFET更好的性能,更低的功耗和更低的泄漏的希望,但它们制造起来更困难且成本更高。

根据Imec的说法,金属间距为3nm时,范围为24nm至21nm。而在3nm处,芯片制造商将继续扩展并在现有材料上使用传统的铜双镶嵌工艺,这意味着RC延迟将仍然在芯片中造成问题。

KLA工艺控制解决方案总监Andrew Cross表示:“当移至3nm节点时,我们将看到BEOL使用多图案EUV以小于25nm的关键Mx间距继续进行缩放。” “这种持续的间距缩放将继续影响线和通孔电阻,因为阻隔材料的厚度缩放比间距慢。”

在研发中,业界继续探索各种新技术,以帮助解决3nm及以上的这些及其他问题。 “在大约24nm的金属间距上,我们预计将开始出现一些有利的设计和材料变化,” Onto Innovation战略产品营销高级总监Scott Hoover说。 “这包括完全自对准的通孔,掩埋的电源轨,supervia集成方案以及更广泛地采用钌衬里。”

电源轨是在BEOL中开发的,是纤巧的结构,旨在处理晶体管中的供电网络功能。 Imec正在开发下一代埋入式电源轨(BPR)技术。在FEOL中开发的BPR埋在晶体管中,以帮助释放互连的路由资源。

另外,该行业还一直在探索在互连件的衬里中使用钌材料。 IBM的Bonilla说:“钌以改善的铜润湿性和填充间隙而闻名。” “尽管钌具有优异的铜润湿性,但它还具有其他缺点,例如电迁移寿命短和化学机械抛光等单元工艺难题。这限制了工业中使用钌衬管。”

即将出现其他新的,更有希望的互连解决方案,但它们可能要等到2023/2024年达到2nm时才会出现。根据Imec的路线图,该行业可以从当今的双镶嵌工艺过渡到2nm的下一代技术,称为混合金属化。将来将采用半大马士革和其他方案。

所有这些都取决于几个因素,即开发新工艺,材料和工具的能力。成本也很关键。

“没有人认为当前的方案可以扩展很多代。 Lam Research计算产品副总裁David Fried表示:“这是通过逐步改进和大量工作来完成的。未来将有更重大的变化,但我预计它们将在不断发展的改进中源源不断地引入。显然,可靠性为缩小层间介电常数k值提供了一些主要障碍,但这一直在继续降低。随着填充材料的变化,对衬里的要求(或什至要有衬里/屏障的要求)也将发生变化。与这些材料相关的工艺将为不同的集成方案(如双大马士革,单大马士革,完全自对准的集成,甚至是减法金属化)带来优点和缺点。在几代之后,BEOL的外观可能会与今天完全不同,但我希望这实际上是所有这些同时发生的更多增量更改的产物。”

尽管如此,对于最紧的层,今天的铜镶嵌工艺将扩展到一定程度。 “双重大马士革一直是个问题。只要我们的间距超过26nm或24nm,这仍然几乎是铜和钴的领域。” Imec纳米互连项目总监Zsolt Tokei说。 “临界点是当您低于20nm间距时。在20nm间距以下,存在许多担忧。这不仅是电阻,而且还涉及可靠性,尤其是对于铜。”

因此,大致在等于2nm节点的间距上,业界希望迁移到称为混合金属化的技术。有人称其为预填充过程。这项技术可能会插入最紧密的层中,但不太关键的层将继续使用传统的铜工艺。

在基本的混合金属化流程中,您将介电材料沉积在基板上。然后,使用传统的镶嵌工艺形成微小的铜通孔和沟槽。然后,您重复该过程,并形成微小的通孔和沟槽。

但是,与其采用双镶嵌工艺,不如说是选择性沉积通孔金属。 Tokei解释说。钼,钌或钨是可以用来填充微小通孔的金属。最后,您完成了常规的铜金属镀层,可以将其视为单个镶嵌铜金属镀层。”

在半导体领域,单金属镶嵌并不是一个新工艺。 “双重镶嵌工艺比单一镶嵌工艺更智能,更具成本效益。随着技术的发展,双金属镶嵌的挑战在于更高和更狭窄的生产线中以及通过组合开口实现无缺陷的铜金属化。” IBM研究人员的主要成员Takeshi Nogami说。 “单金属镶嵌将这两种图案分离以进行金属化,使其更容易缩小宽度和间距尺寸,并提高线宽比,以减轻电阻的上升。”

总而言之,混合金属化在互连中使用两种不同的金属。 Imec的Tokei说:“对于2nm,这至少在一层上是很有意义的。”与双镶嵌相比,通孔电阻更低。您的可靠性将会提高。同时,我们可以保持线路中铜的低电阻率。”

但是,混合金属化存在一些障碍。有几种不同且困难的沉积技术可以实现间隙填充过程。 M.H.说:“挑战在于如何在不损失选择性的情况下实现良好的通孔填充均匀性。”台积电(TSMC)研究员Lee在IEDM上发表论文。 “此外,通孔侧壁是无障碍的,通孔材料与底层金属之间的潜在相互作用可能会导致可靠性问题。”

什么是半大马士革?如果业界能够解决这些问题,则可以在2nm处插入混合金属化层。但是,如果要继续扩大芯片规模,业界可能需要2nm以外的另一种解决方案。

超越2nm,下一步是许多人所说的半镶嵌工艺,这是一种针对最紧的金属间距的更彻底的技术。在研发中,由于多种原因,该行业正在探索半大马士革。

TEL技术人员高级成员Robert Clark说:“在双重镶嵌结构中,生产线的数量是铜晶粒生长的限制因素。” “相反,如果通过沉积可退火的金属层形成金属线,然后通过蚀刻形成金属线,则可以增加晶粒尺寸。但是对于铜来说,这种过程很难实现。像钌这样的金属在这种处理过程中要容易得多,因此它有可能实现人们所说的半镶嵌处理。”

半大马士革的起点是20nm以下的间距。 “我们的目标是在18nm以下的半大马士革。因此,也许像是从现在起的四五年后。” Imec的Tokei说。 “这对逻辑工厂来说是破坏性的。建立了一个用于铜金属化和双镶嵌的晶圆厂。混合金属化几乎自然地落入该流中。您需要一些用于预填充本身的新功能。但是对于其余部分,您可以重用晶圆厂中的所有东西。”

半大马士革需要使用新工具的不同工艺流程。简而言之,半大马士革可实现带有气隙的微小通孔,从而减少了芯片中的RC延迟。

该技术依赖于使用替代蚀刻工艺的金属图案化。替代蚀刻不是新技术,用于较旧的铝互连工艺。但是,要在2nm以上的范围内实施该技术存在一些挑战。

“半大马士革工艺始于对通孔进行构图并将其蚀刻到介电膜中。然后,用金属填充通孔并对其进行过度填充,这意味着金属沉积将继续进行,直到在电介质上方形成一层金属为止。然后对金属进行掩膜和蚀刻,以形成金属线。” Tokei在最近的博客中说。

在实验室中,Imec设计了一种基于64位Arm CPU的12金属层设备。该器件具有两层使用钌材料的金属互连。金属线之间形成气隙。

Tokei说:“气隙显示了将性能提高10%的潜力,同时将功耗降低了5%以上。” “使用长宽比高的导线可以将电力网络中的IR下降降低10%,以提高可靠性。”

但是,半大马士革远未准备就绪。 Tokei在最近的一篇论文中说:“半金属镶嵌方案存在许多潜在的问题,例如对准,金属蚀刻,LER,泄漏,芯片封装相互作用,密封环兼容性,等离子体损伤和可布线性。”

结论其他的互连技术正在研发中,例如超导通孔,金属-石墨烯混合互连以及铜的替代品。

但是可以肯定的是,由于下一代技术面临若干挑战,因此业界宁愿尽可能延长铜双镶嵌。

在某个时候,该行业可能需要下一代互连技术。芯片制造商可能会找到解决方案。但是,如果做不到,那么传统的芯片扩展可能就束手无策了,这迫使业界寻找替代解决方案来实现高级芯片。

那已经发生了。 Momentum已经在为高级包装而建造,这是使开发人员能够使用的另一种方法

......