新兴应用和高级包装挑战

先进封装在开发新的系统级芯片设计中扮演着越来越重要的角色,并成为一种更可行的选择,但它也为芯片制造商提供了一系列令人困惑的选择,有时价格也很高。

汽车,服务器,智能手机和其他系统已经采用一种或另一种形式的高级包装。对于其他应用程序来说,这太过分了,简单的商品包装就足够了。尽管如此,高级包装正迅速成为许多人的诱人选择。业界正在开发新形式的高级封装或升级现有技术,以用于5G和AI等一系列应用。

达到这一点已经花费了行业多年的时间。几十年来,可以将模具组装成基本包装。但是,随着规模逐渐枯竭,封装提供了一套全新的架构选择,可以提高性能,降低功耗并为设计增加灵活性,从而既可以针对特定市场进行定制,又可以缩短上市时间。

但是,没有一种包装类型可以满足所有需求。每个应用程序都是不同的,每个都有其独特的要求。在某些情况下,高级包装甚至可能不是正确的解决方案。

半导体工程公司研究了高级包装在四个市场中的优势和挑战:服务器,网络设备,智能眼镜和军事/航空航天。尽管这只是可能应用的示例,但它突出显示了芯片制造商未来将在封装方面面临的一些主要问题和挑战。

根据YoleDéveloppement的数据,2019年整个IC封装市场价值680亿美元。根据Yole的说法,其中高级包装行业在2019年为290亿美元,预计将增长6.6%,到2025年达到420亿美元。

服务器通常,为了推进领先的设计,设备制造商需要依靠芯片扩展。目标是在每个新的工艺节点上的单片芯片上封装更多功能,新节点大约每18到24个月推出一次。但是在每个节点上扩展变得越来越困难和昂贵,并且价格/性能优势正在减少。因此,尽管扩展将继续进行,但并非系统中的所有组件都将同样进行扩展。

联华电子业务发展副总裁伍尔特说:“这实际上与经济学有关。” “在尖端节点,晶圆成本是天文数字,因此,很少有客户和应用程序能够负担得起昂贵的工艺技术的费用。即使对于负担得起成本的客户,他们的某些裸片尺寸也正在与最大标线片尺寸相抵触。当然,这导致了产量挑战,从而进一步加剧了成本问题。客户需要更优化的技术解决方案,它将提供更具成本效益的业务解决方案。从上市时间的角度来看,对于许多人来说,在前沿设计和验证大型片上系统(SoC)所花费的时间也是一个问题。”

在服务器世界中,这既指向分解(不需要最先进的数字逻辑或从中受益的卸载功能),也指向使用高速管芯对管芯互连的异构集成。有许多选项可用,但当前的话题是小芯片。

在小芯片中,芯片制造商可以在一个库中具有一个模块化管芯或小芯片的菜单,并非所有模块都必须在同一工艺节点上开发。通常,包含小芯片的设计类似于单片SoC,但是开发成本较低。

在纸面上听起来一切都很好,但是仍然存在一些挑战。 “这是一个新兴的环境。这是一种新模式。接口方面没有很多标准。小芯片集成的最早采用者往往是可以控制所有设计元素,特别是界面的垂直集成公司,” ASE的业务开发高级总监Eelco Bergman在最近的IMAPS2020会议上的演讲中说。 “如今,小芯片设计将主要由芯片开发者推动,无论是IDM还是无晶圆厂供应商。随着行业的发展和生态系统的开放,您会看到这种变化。”

其他人表示同意。 “了解总线设计和接口规格非常关键。如果是专有情况,那么显然客户最终将在那里担任领导角色。这将在一段时间内成为现实,” Amkor高级封装和技术集成副总裁Mike Kelly在演讲中说。 “一旦我们建立了一个大家都可以理解并且规格明确的通用总线架构,那么无论是垂直整合公司,IDM还是OSAT,设计都可以非常灵活。”

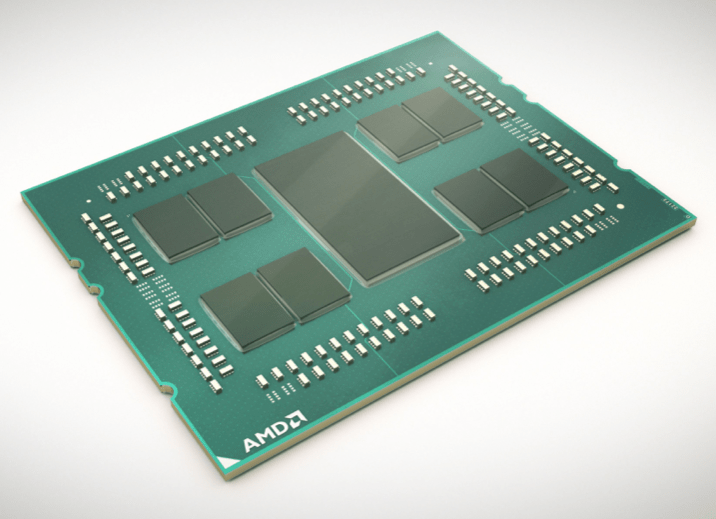

AMD,英特尔和其他一些公司已经引入了类似芯片的架构。例如,AMD最新的服务器处理器系列取代了大型的单芯片,将较小的芯片集成到了一个模块中,该模块有时称为多芯片模块(MCM)。使用管芯到管芯互连来连接芯片。

AMD的MCM被称为2D小芯片设计,它基于14nm工艺集成了集成的I / O和内存控制器芯片。那个死在中间。 MCM中还集成了八个7nm处理器管芯。四个处理器管芯位于I / O管芯的每一侧。

图1:具有8个核心芯片和1个I / O芯片的AMD EPYC服务器过程资料来源:AMD

由于服务器处理器产品线的原因,AMD转向了类似小芯片的方法。 “为了维持每两年2倍性能所要求的性能趋势,我们将需要小芯片,不仅要以更高的良率实现更多的晶体管,还要减少先进节点硅的总量,” Bryan Black说, AMD的高级研究员在演讲中

展望未来,AMD计划在服务器处理器方面扩大其MCM工作。它还计划使用3D堆叠技术开发小芯片。布莱克说:“随着我们进入3D堆叠,我们将加剧我们一直在以2D方式进行的所有这些挑战。”

基于2D和3D的小芯片设计都面临许多相同的挑战。布莱克说:“小芯片不是免费的。” “它们确实具有与之相关的成本,包括包装成本和模具面积成本的增加。我们不能采用面积为2倍的单片组件,并将其分成两个较小的裸片,每个面积仅为1倍。两者之间的通信以及其他的电源逻辑,其他的一致性逻辑,其他的时钟控制以及有效的测试控制,都将产生开销。除了连接这两个裸片并使它们看起来尽可能像一个裸片所需的I / O通信开销外,我们还有大量的额外控制逻辑。”

最重要的是,封装需要具有良率的模具,也称为已知的良模具。封装中的一个坏晶粒可能导致产品或系统故障。 “所有模具都有参数变化。因此,我们遇到了多管芯解决方案的基本测试和特征化问题。有些很慢。有些很快。有些会消耗更多或更少的电量。”布莱克说。

热量,功率分配和可靠性也是基于小芯片设计的挑战。然后,如果打包失败,那么最大的问题就是谁来负责。是芯片供应商,IP供应商还是封装厂?

为此,包装行业可以借鉴过去的经验,尤其是在2.5D的早期阶段。使用2.5D时,管芯堆叠或并排放置在中介层的顶部。内插器结合了硅通孔(TSV),充当芯片和电路板之间的桥梁。

在2.5D的早期阶段,设备制造商一直在努力应对不同的模具,集成问题和成品率挑战。但是,随着时间的流逝,供应商解决了这些问题。

“我记得2.5D项目是何时开始的,” Amkor的凯利说。 “帮助我们的第一件事就是提高产量。然后,对您所遭受的少量产量损失进行分类并不是一个巨大的挑战。”

如果管芯不符合规格,供应商将对设备进行广泛的根本原因分析。这需要一个完善的测试策略。

可以使用小芯片为同种集成实现相同类型的配方。和以前一样,开发出合格率高的模具至关重要。 “您将把它带到另一个极端。您将拥有更多的模具和更多的焊点。但是,只要您的基本组装过程牢不可破,就不会像我们在2.5D上发现的那样痛苦地进行讨论。” Kelly说。

实际上,包装必须以可接受的成本具有良好的产量。但是,当发生故障时,它可以返回给供应商。 “归根结底,供应商是最终负责产品的供应商。但是支持该芯片供应商的供应商可以在该故障分析过程中提供帮助。一旦确定了这一点,负债和责任就会更加清楚。” ASE的Bergman说。

目标是首先预防故障。从设计开始,需要采取整体方法。 Quik-Pak首席运营官Ken Molitor说:“在设计阶段,我们将找出最适合客户的方案。” “我们将交钥匙整个项目,在那里我们要设计基板,制造基板,然后提出具有凝聚力的设计。然后,我们将其组装。 (在此过程中,有一些里程碑。)这往往会降低他和我们的风险。”

网络设备网络设备供应商面临许多相同的挑战。网络是一个复杂的系统,范围从家庭办公室到云。为了应对这些市场,通信设备供应商针对网络的各个部分出售不同的系统。

例如,在网络的一部分中,思科为大型服务提供商出售路由器。路由器使用IP数据包定向网络。思科最新的路由器基于其自己的内部ASIC。思科的单片ASIC围绕7纳米工艺构建,可在同一芯片上实现12.8 Tbps的带宽。

思科还为其其他网络产品开发ASIC。其他通信设备供应商也开发ASIC。

出于多种原因,供应商也在探索或实施替代方法。在每个节点上,ASIC变得越来越大,越来越昂贵。它还集成了SerDes(串行器/解串器),可提供高速的芯片到芯片通信。

Juniper的资深工程师Valery Kugel在演讲中说:“网络带宽扩展要求导致每一代技术的联网ASIC芯片尺寸都会增加。” “(SerDes)占据了ASIC的很大一部分。”

还有其他问题。 ASIC由数字和模拟模块组成。数字部分得益于扩展功能,可在更高带宽下实现更多功能。但是,并非所有事情都能从扩展中受益。

“ SerDes功能没有减少。那是一个模拟结构。它的伸缩性不好。” TE Connectivity的技术专家兼行业标准经理内森·特雷西(Nathan Tracy)说。 Tracy还是行业标准组织光学互联网络论坛(OIF)的主席。

这里有几种解决方案,包括小芯片。为了将芯片连接到封装中,OIF正在开发一种称为CEI-112G-XSR的芯片对芯片接口标准。 XSR连接MCM中的小芯片和光学引擎。它可通过短距离链路实现高达112Gbps的数据速率。 XSR仍处于草稿形式。

有几种方法可以在网络设备中实现小芯片和XSR。例如,大型ASIC分为两个较小的管芯,这些管芯使用XSR链接进行连接。

在另一个示例中,大型SerDes模块被分解为四个较小的I / O芯片。然后,在MCM中,ASIC位于中间,中间被四个较小的I / O小芯片包围。

另外,设备制造商可以将光学引擎与MCM中的交换芯片ASIC集成在一起。

特雷西说:“业界对于共封装光学器件的讨论很多。” “我说的是从交换机面板上的可插拔光收发器转移到直接将光学引擎安装在交换硅上的可能性。您需要低功耗高速互连。讨论的重点是OIF的XSR开发。”

小芯片的采用将取决于应用程序。在某些情况下,ASIC仍然有意义。这里有几个因素,例如成本和产量。特雷西说:“这一切都是为了减少功耗。”

“使用小芯片可以减小主芯片的尺寸,使其符合掩模版的尺寸限制。”但是,大多数集成电路不受标线限制。因此,该论点仅适用于极少数的IC。一位专家表示,这是一个很强的论点,不适用于大多数设计。 “如果将设计分成两部分,则每个晶片的裸片数量将是原来的两倍。假设每个晶圆的缺陷“ D”相对恒定,那么您的良率便从X-D变为2X-D。当然,每个封装需要的裸片数量是原来的两倍,因此您的有效成品率为(2X-D)/ 2 = X-D / 2。您已经有效地将缺陷减少了一半,而使用的是两个模具相比一个模具更复杂的封装。随着多管芯封装技术的不断发展,这将不再是一个问题。”

智能眼镜这些解决方案可能适用于网络设备,但是消费市场有不同的要求,尤其是对于新兴产品。

例如,在研发中,几家公司正在开发下一代智能眼镜或AR / VR眼镜。虚拟现实(VR)使用户可以体验3D虚拟环境。增强现实(AR)拍摄计算机生成的图像,并将其覆盖在系统上。

如果这项技术可行,AR / VR眼镜可以用于数据检索,面部识别,游戏和语言翻译。他们还可以将演示文稿或键盘投影在表面上。

Facebook Reality Labs的主任兼研究科学家Liu Chiao在去年IEDM上的一篇论文中表示:“ [AR / VR]及其变体设备才刚刚成为成为下一代计算平台的旅程的起点。”

开发一副有用且便宜的智能眼镜并不是一件容易的事。这些产品需要新的低功耗芯片,显示器和接口。在这些眼镜中,程序是使用语音,视线和头部/身体移动来激活的。所有这些技术必须是安全的。

“我们将需要全面改善,” Facebook的硅工程主管Ron Ho在IMAPS2020上的演讲中说。 “相对于电源,我需要的性能要比当今系统所能维持的性能高得多。通常,我需要以较低的延迟更快地运行事情。”

为了以合适的尺寸实现智能眼镜,IC封装是关键。 Ho说:“我必须管理能够提高性能和降低延迟的软件包。” “您不能强迫芯片经过多英寸的走线并在PCIe上消耗大量功率。但是,您可以将它们共同包装,然后彼此放置。通过TSV,它们具有更高的带宽和更高的性能连接。”

在IEDM上,Facebook透露了有关其AR / VR眼镜的一些线索,这些线索正在研发中。 Facebook在一篇论文中概述了用于AR / VR眼镜的计算机视觉接口技术的发展。基础技术是先进的CMOS图像传感器。

CMOS图像传感器在智能手机和其他产品中提供相机功能。但是标准的图像传感器不足以用于AR / VR眼镜。所需要的是具有先进包装的机器感知优化图像传感器。 Facebook在论文中描述了一种三层图像传感器。第一层是具有处理单元的图像传感器,其后是聚合处理器,然后是云计算平台。

Facebook还提到了铜杂化粘合。为此,使用铜-铜扩散键合技术将管芯堆叠并连接。目前尚不清楚Facebook是否会走这条路,但是混合绑定是图像传感器领域的一项已知技术。

军事/航空航天与此同时,几十年来,美国国防部(DoD)认识到芯片技术对于美国的军事优势至关重要。对于各种系统,国防界在高级节点和成熟节点上都使用芯片。包装也是方程式的关键部分。

军事/航空航天涉及众多具有不同要求的客户,尽管这里有一些共同的主题。 Quik-Pak的Molitor说:“我们为许多不同领域提供服务。” “我们确实为军用/航空业服务。军事/航空计划往往是长期存在的。它们习惯于处理必须工作20到30年的组件。”

军用/航空客户面临其他挑战。与商业领域一样,开发高级芯片的成本昂贵,但每个节点的收益却在缩小。另外,国防部门的数量相对较少。

有时,国防界使用非美国铸造厂来获得高级芯片,但出于安全目的,它更倾向于使用在岸供应商。军用/航空业客户希望获得可信赖且有保证的芯片和封装供应链。

尽管如此,国防部仍在寻找芯片扩展以外的替代方法,即异构集成和小芯片。

例如,英特尔最近获得了国防部新芯片工作的新合同,称为最新异构异构原型(SHIP)计划。根据该计划,英特尔围绕小芯片建立了一个新的美国商业实体。该计划使客户可以使用英特尔的包装功能,包括国防部和国防界。

SHIP程序包含多个部分。当英特尔赢得该计划的数字部分时,Qorvo被授予了SHIP项目的RF部分。在该项目下,Qorvo将在德克萨斯州建立一个射频异构包装设计,生产和原型制作中心。该中心将主要为国防界服务。

Qorvo对mil / aero并不陌生。多年来,RF设备和其他产品的供应商为mil / aero和商业领域提供铸造和包装服务。该公司开发基于氮化镓(GaN),砷化镓(GaAs)和其他工艺的器件。

多年来,以密尔/航空为单位的包装要求已经发生了变化。 “多年前,我刚开始为Qorvo工作时,没人希望我们将包装好的零件寄给他们。 Mil / aero希望裸机,” Qorvo国防和航空航天市场战略总监Dean White说。 “我们已经看到了市场从军事裸露的航空航天市场到包装和包装集成的转变。包装比几年前更加环保。我们根据功率水平,散热和抗振能力,以多种不同的包装为军用/航空业进行大量包装。”

根据SHIP计划,Qorvo将使用基于GaN,GaAs和硅的器件提供异质封装服务。目的是满足国防部所称的SWAP-C,这是一个首字母缩写,表示相控阵雷达系统,无人驾驶车辆,电子战平台和卫星等各种应用中包装的尺寸,重量,功率和成本要求。

尽管Qorvo将提供一站式服务,但SHIP计划是针对包装的。它将继续为军事/航空业的客户提供铸造和包装服务。 “我们以铸造模型为模型。我们使用的是同一类型的模型。这将是一项服务。您可以在我们的铸造厂进行设计。然后您可能会说,‘您可以将这些零件放入包装中吗?’这是对我们当前能力的补充或扩展,”怀特说。

同时,mil / aero涉及定制工作。每个客户可能对包装有不同的要求

......