引导加载如何使历史性的Intel 8008处理器成为可能

大约在1972年底,英特尔推出了他们的第一个8位微处理器8008。十年后,这个处理器仍然影响着计算;您可能使用的x86处理器是8008的后代。8008处理器的一个不同寻常的特点是它使用了自举负载或自举电容器,这是一种特殊的电容电路来提高性能。1费德里科·法金是这个故事的主角,他领导了8008的开发;他发明了一种新的方法,为英特尔4004和8008处理器制造自举电容器,并说事实证明这对微处理器的实现至关重要。没有[自举加载],就没有微处理器。

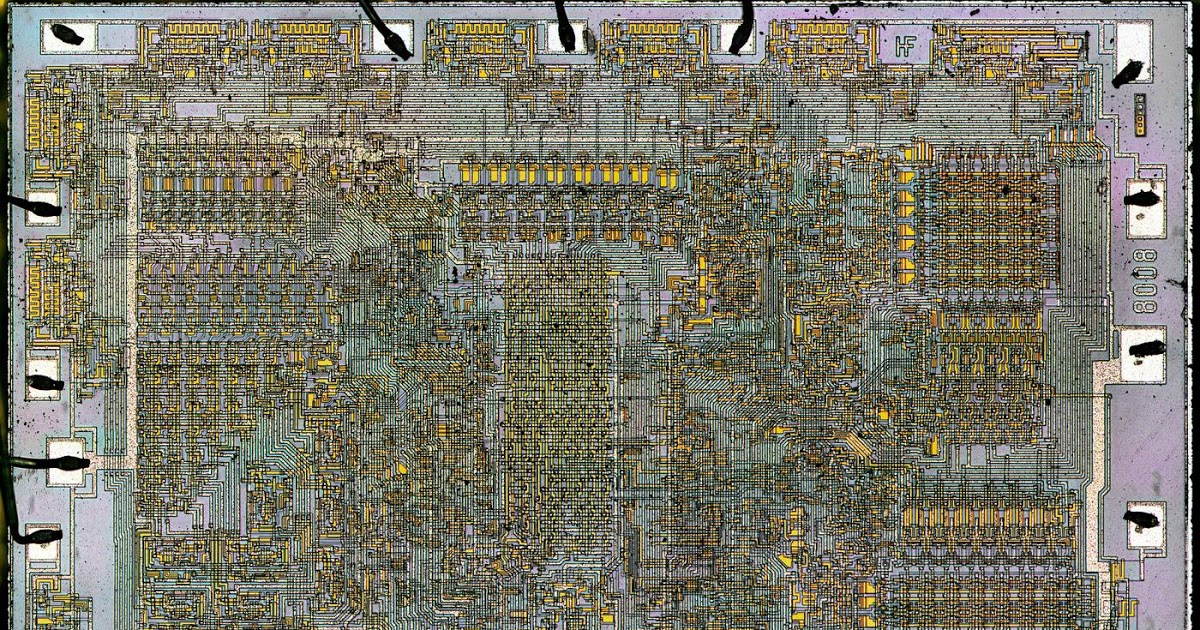

8008微处理器的模具照片。(点击查看大图。)右上角出现了Hal Feeney的名字缩写HF,他负责芯片的逻辑设计和物理布局。

我上面的照片显示了8008封装内部的微小硅芯片。你几乎看不到构成芯片的导线和晶体管。有90个自举电容器,可以看到黄色的小矩形,特别是在上面的中心。外面的正方形是通过微小的焊线连接到外部引脚的18个焊盘。18个引脚对于微处理器来说是一个非常小的数字,但英特尔当时奇怪地致力于小封装。2这需要进行不方便的权衡;缺少多个电源引脚是强制使用自举负载的一个因素。

8008处理器';的历史比你想象的要复杂得多。它的根源是DataPoint2200,这是1970年作为可编程终端引入的一种流行的计算机。DataPoint2200在微处理器出现之前被创造出来,它包含一个电路板大小的CPU,由单个TTL芯片组成。Datapoint与英特尔和德州仪器讨论了用单一MOS芯片取代处理器板的问题。德州仪器在1971年3月创造了TMX 1795处理器,而英特尔在1971年底左右创造了8008,但Datapoint因为各种原因拒绝了这两种芯片。德州仪器在试图将TMX 1795推向市场失败后放弃了TMX 1795。另一方面,英特尔将8008作为通用微处理器进行了销售,但由于种种原因,英特尔在1971年底左右发明了8008,但由于种种原因,Datapoint放弃了TMX 1795。另一方面,英特尔将8008作为通用微处理器进行了销售。创造微处理器产业。

(您可能想知道Intel4004是如何融入这个故事的。Intel4004在体系结构上几乎在所有方面都与8008无关;尽管名称相似,但8008不是4位4004的8位版本。1971年Intel4004推出后,4004团队的大部分成员(包括Faggin、Hoff、Mazor和Feeney)转移到8008项目。由于4004和8008处理器是由同一个团队用相同的PMOS3工艺制造的,它们在布局和电路级上有一些相似之处,特别是引导加载电路。)。

自举负载的目的是在必要时从晶体管获得额外的电压。为了解释这一点,我将首先说明逆变器在处理器中实现时是如何工作的。下图显示了一个由PMOS 3晶体管和负载电阻(实际上是晶体管)组成的逆变器。如果逆变器的输入为0(低),则较低的晶体管接通,将输出拉高(1)。但如果输入为1(高),则输出晶体管关闭。在这种情况下,负载电阻器将输出拉低(0),从而使输入信号反转。

逆变器是如何由PMOS晶体管构成的。上面的符号表示充当负载电阻的PMOS晶体管。基于8008数据表。)。

下图显示了8008处理器中逆变器的物理实现。第一张芯片照片显示了逆变器在芯片中的外观。顶部的水平金属布线提供VDD和电路的输入。对于第二张照片,我溶解了金属层,显露出构成电路的两个晶体管。右边的原理图与芯片上晶体管的物理布局相匹配,但在其他方面与上面的原理图相对应。由于在集成电路中创建电阻不方便,负载电阻器由晶体管实现。

使用晶体管作为负载电阻有一个复杂之处:这些MOS晶体管有一个叫做阈值电压V_T的特性。问题是,当你试图把信号拉低时,晶体管不能把它一直拉低。虽然你想把信号拉低到V_DD(-9伏),但是阈值电压(比方说-5伏)9意味着你只能把信号降到-4伏。(这也是为什么8008需要比现代集成电路高得多的电压(总电压为15伏)的原因之一,因为你想要把信号拉低到-4伏。这就是为什么8008需要比现代集成电路高得多的电压(总电压为15伏)的原因之一,但阈值电压(比方说-5伏)9意味着你只能把信号降到-4伏。(这就是为什么8008需要比现代集成电路高得多的电压(总电压为15伏)的原因之一。如果您尝试在5伏电压下运行,阈值电压将消耗整个信号。)。

下图更详细地解释了阈值电压。VD、VG和VS分别是漏极、栅极和源极上的电压。VGS是栅极和源极之间的电压。如果VGS<;VT是阈值电压,晶体管就会导通。(不便的是,在PMOS晶体管中,这些电压大多是负的,这使得事情变得混乱。)问题是,在栅极电压为-9V和阈值电压为-5V的情况下,只有当VS高于-4V时,晶体管才会导通。因此,晶体管可以#39;将VS降低到-4伏以下。降低VS的唯一方法是使用更负的栅极电压,在这种情况下至少为-14伏。一些芯片通过使用额外的电压源来为栅极提供更高的电压来解决这个问题,例如Intel 8080或HP Nano Processor。

V_D、V_G和V_S分别是晶体管的漏极、栅极和源极上的电压。Vgs是栅极和源极之间的电压差。

当你与反相器和其他门打交道时,阈值电压不是什么大问题,因为电压电平是由每个门恢复的。但是,阈值电压有两个地方有问题:超级缓冲器和通路晶体管逻辑。在这些电路(在脚注4中描述)中,阈值电压下降发生两次,导致输出太弱。由于这些电路在处理器中很常见,因此需要一个解决方案:自举负载。这是一种为栅极产生更多电压的方法,以克服阈值电压,因此晶体管将其输出拉到VD的方式。

自举负载本质上是一个电荷泵电路,它使用自举电容器来提升栅极电压。下图显示了电荷泵的基本概念。在左边,电容器从电压源充电到-9伏。如果断开电压源,然后将负端重新连接到电容器,如右边所示,电容器将保持-9伏的电荷。但是,由于电容器的下侧现在是-9伏,电容器的上侧现在是-18伏。自举负载使用这个-18伏作为栅极电压,足以克服阈值电压。

充电泵。在左边,电容器充电到-9伏。在右边,电容器的底部连接到-9伏,在电容器的顶部产生-18伏。

下图显示了自举负载电路。该电路类似于前面描述的逆变器,但增加了一个电容器和一个晶体管。在第一个图中,0输入接通较低的晶体管(Q1),产生1输出(+5伏)。同时,Q3充当负载电阻,将电容器的顶部拉到-4伏(而不是阈值电压导致的-9伏)。这导致电容器上存储的电压为-9伏。

第二个和第三个图表显示输入为1时会发生什么情况。较低的晶体管Q1关断,允许Q2将输出拉低。对于常规的逆变器,-4伏是输出所能达到的最低电压(第二张图)。但是,如前所述,电容器仍然保持-9伏,所以电容器的顶部必须是-13伏。当Q2的栅极上有-13伏时,Q2将继续拉低输出,直到电路结束,如右图所示,输出一直拉到-9伏。请注意,电源可以';I don‘不管栅极电压如何,都不会低于漏极。(相比之下,前面描述的简单逆变器只能将输出拉低到-5伏。)5.(与之相比,前面描述的简单逆变器只能将输出拉低到-5伏。)

下图显示了英特尔4004处理器原理图的一部分,其中显示了用于标准负载的电路和用于引导负载的电路,由电阻器旁边的A#34;B#34;表示。

英特尔4004原理图上的引导加载表示。带#34;B&34;的电阻器表示其旁边的自举加载电路。

到目前为止,我已经讨论了自举负载,它广泛用于MOS电路,并于1966年由北美罗克韦尔公司申请专利。4004和8008处理器所必需的发明是将自举负载扩展到硅栅集成电路。

使8008实用化的关键发明之一是自对准硅栅晶体管。6下图显示了MOS晶体管的结构。早期的MOS集成电路使用金属栅晶体管,这种晶体管使用金属,通常是铝,而不是多晶硅作为栅极。但是在1968年的费尔柴尔德会议上,Faggin和Klein发明了一种实用的方法来制造硅栅晶体管。这看起来似乎差别不大,但硅栅晶体管在三个重要方面比金属栅晶体管要好得多。首先,硅栅晶体管的电性能比金属栅晶体管好得多,运行速度更快,功耗更低。第二,多晶硅为路由信号提供了第二层,使集成电路布局更加紧凑。

最后,多晶硅允许自对准晶体管的构建,它在旁路电容中起着重要的作用。集成电路是通过一系列工艺步骤来构建的,使用光学掩模和光敏抗蚀剂在表面上产生图案。具有金属栅晶体管的集成电路是自下而上构建的。首先,在源极和漏极区域掺杂杂质以形成P型硅,如下所示。在后面的步骤中,使用不同的掩模在源极和漏极之间创建金属栅极。棘手的部分是确保栅极与源极和漏极对齐;如果有#39;如果是间隙,晶体管就不会工作。因此,金属栅会比需要的更大,所以即使层的对准稍有偏差,它仍能覆盖栅沟道。不幸的是,这种重叠会产生电容并损害性能。

另一方面,自对准闸门是以相反的顺序创建的。首先创建多晶硅栅极,在随后的步骤中,对源区和漏区进行掺杂。然而,掩模并不是用来将源极和漏极与栅极分开的。相反,栅极本身会阻止源极和漏极之间区域的掺杂。因此,源极和漏极会自动与栅极对齐,从而消除过大栅极带来的过剩电容。(为什么金属栅极不能自对准呢?)。因为掺杂硅需要较高的温度才能熔化金属,但多晶硅可以处理热量。)。

虽然自对准硅栅是对金属栅的重大改进,但有一个缺点:电容。使用金属栅晶体管,可以很容易地用金属和掺杂硅作为极板来构建电容器:顶部是大金属层,下面是掺杂硅,中间是薄的绝缘氧化层。(换句话说,使用带有大栅的晶体管作为电容器。)有了自对准栅,多晶硅栅可以用来代替金属层作为电容器板。然而,在自对准过程中,多晶硅栅会阻碍下面硅的掺杂。在自对准过程中,多晶硅栅会阻碍下面硅的掺杂。在自对准工艺中,多晶硅栅会阻碍下面硅的掺杂。在自对准工艺中,多晶硅栅会阻止下面硅的掺杂。在自对准工艺中,多晶硅栅会阻止下面硅的掺杂。在自对准工艺中,多晶硅栅会阻止下面硅的掺杂,这对抗电阻器有利,但对电容器不利,因为你可以';不要在多晶硅板下面掺杂硅。(你可以在制造多晶硅栅前使用额外的制造步骤来掺杂电容板,但是这个额外的步骤会增加成本。)。

Faggin发明了一种解决方案,使电容器具有自对准栅极的实用性。他意识到,如果你正确地偏置电容器,即使没有任何掺杂,上极板上的电荷也会在它下面的硅上形成一个导电区。他在仙童进行了尝试,发现它很有效,这解决了如何使用自对准硅栅晶体管的自举负载的问题。

上图放大了用于逆变器的8008的其中一个自举加载电路。下图显示了去掉金属层后的底层硅。自举电容器是由底层硅上的一层多晶硅(粉红色)构成的,形成了电容器板。右边的晶体管使输入反转。电容器由左下角的晶体管充电。负载晶体管位于中间,电容器向其栅极提供升压。根据其作用,晶体管有不同的大小。逆变晶体管是最大的,因为它提供最大的电流。与之相比,给电容器充电的晶体管非常小,因为小电流就能使电容器保持充电。

这种自举加载技术在4004和8008处理器中广泛使用。下图显示了8008处理器中的自举加载,用红框表示。8008有90个自举加载,因此它是一个重要的电路。许多自举加载位于芯片外围,以帮助驱动输出引脚。指令寄存器(中上方)使用自举加载来驱动相对较大的指令解码器(中间)。在右侧,自举加载驱动寄存器存储(右上角)和堆栈存储(右下角)。整个处理器中的其他杂项电路也使用自举加载。

最后一个问题是,引导加载是否是使微处理器成为可能的关键发明(如4004和8008中所体现的),或者微处理器是否不可避免,而不考虑诸如引导加载之类的特征。一种观点认为,埋入地下的触点,尤其是引导加载,对于在可用功率预算内获得所需的速度是不可或缺的。Feeney在8008口述历史中说,由于管脚和电源等方面的限制,引导加载变得非常关键。另一方面,微处理器的开发对许多人来说似乎是一个不可避免的渐进过程。仙童的工程师李·博伊塞尔在1970年说过,片上计算机并不是什么大不了的事。它现在就快到了……。毫无疑问,在五年内,整个计算机将集中在一块芯片上。英特尔的哈尔·费尼说,20世纪70年代初,60年代末,该行业发明微处理器的时机已经成熟。

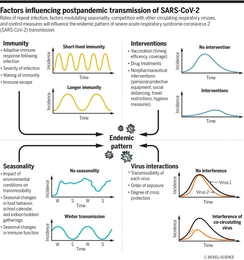

在狭义意义上,自举负载使4004和8008在给定的尺寸、性能和功耗下成为可能。自举负载也说明了微处理器不是单一的发明,而是使其成为可能的许多较小发明的集合。然而,从更广泛的角度来看,如果自举电容不是#39,微处理器将只会受到轻微的阻碍。存在。有许多替代方案,例如四相逻辑、静态逻辑、更高的栅极电压、额外的电源,或者为电容器使用额外的掩模。德州仪器公司的TMX 1795提供了直接的比较,因为它是与8008同时建造的,具有相同的体系结构,但使用金属栅极晶体管而不是硅栅。下图显示TMX 1795比8008大得多,并且它的性能略差,但要点是,在没有引导加载的情况下,微处理器的运行基本上是相同的。在任何情况下,到1974年,切换到NMOS晶体管和阈值电压的改进使得自举负载变得不必要,我的结论是自举负载是一项有益的创新,但即使没有本发明,微处理器也会沿着类似的路径前进。一旦技术允许在一块集成电路上建造几千个晶体管,单片CPU就不可避免了。

比较TMX 1795、4004和8008微处理器的芯片尺寸。请注意,4004和8008的大小几乎相同,而TMX 1795的大小则是前者的两倍多。TMX 1795的上三分之一是指令解码和控制逻辑,中间是8位ALU,底部是存储(堆栈和寄存器)。TMX 1795模具照片由计算机历史博物馆提供。

如果你对8008感兴趣,我之前的文章详细讨论了8008的架构和更多的芯片照片;我还解释了8008的ALU。我在Twitter上宣布了我最新的博客帖子,所以请在kenshriff上关注我。我还有一个RSS订阅源。

在他的口述历史中,费金描述了英特尔对16针封装的执着。当一个存储芯片需要18针而不是16针时,就像天空从天而降一样。我从来没有在英特尔看到过这么多关于这个问题的长脸,因为这是英特尔的一种信仰;在那个时代,所有的东西都必须是16针的。所有东西都必须是16针...。这是一个完全愚蠢的要求,16针。";当时,其他制造商正在使用40针和48针封装,所以没有技术限制,只有一个

超级缓冲器用有源晶体管代替负载电阻,并在需要更多电流时使用,例如驱动内部总线或输出引脚。上部晶体管由逆变器驱动,因此在下部晶体管关闭时接通。该晶体管提供高电流,而不是来自负载电阻/晶体管的弱电流。问题是阈值电压限制了来自上部晶体管的电压。使用常规逆变器,逆变器输出的电压会损失VT,因此它将向上部晶体管提供-4伏特电压,而不是来自负载电阻器/晶体管的弱电流。#34;超级缓冲器会用有源晶体管代替负载电阻,并在需要更多电流时使用,例如驱动内部总线或输出引脚。上部晶体管由反相器驱动,因此在下部晶体管关断时接通。该晶体管提供高电流,而不是来自负载电阻/晶体管的弱电流。问题是阈值电压限制了来自上部晶体管的电压。在那里失去另一个VT将产生不足的+1伏的输出电压,而不是所需的-9伏。

阈值电压降是问题的第二种情况是用于动态逻辑的通路晶体管,下图显示了一个简单的通路晶体管电路。当控制信号为低时,晶体管被激活,将输入信号传递到输出。但当控制信号为高时,晶体管停止通过输入。相反,先前的值由电路的电容(以灰色显示)保持,因此输出保持其先前的值。因此,通路晶体管提供了一种实现临时存储的有效方式。通路晶体管的问题是阈值电压。如果栅极上的控制信号来自常规栅极,则由于阈值电压损失,导通电压将为-4伏。传递晶体管导致第二阈值电压损失,因此它可以拉出的最低阈值电压损失。

.