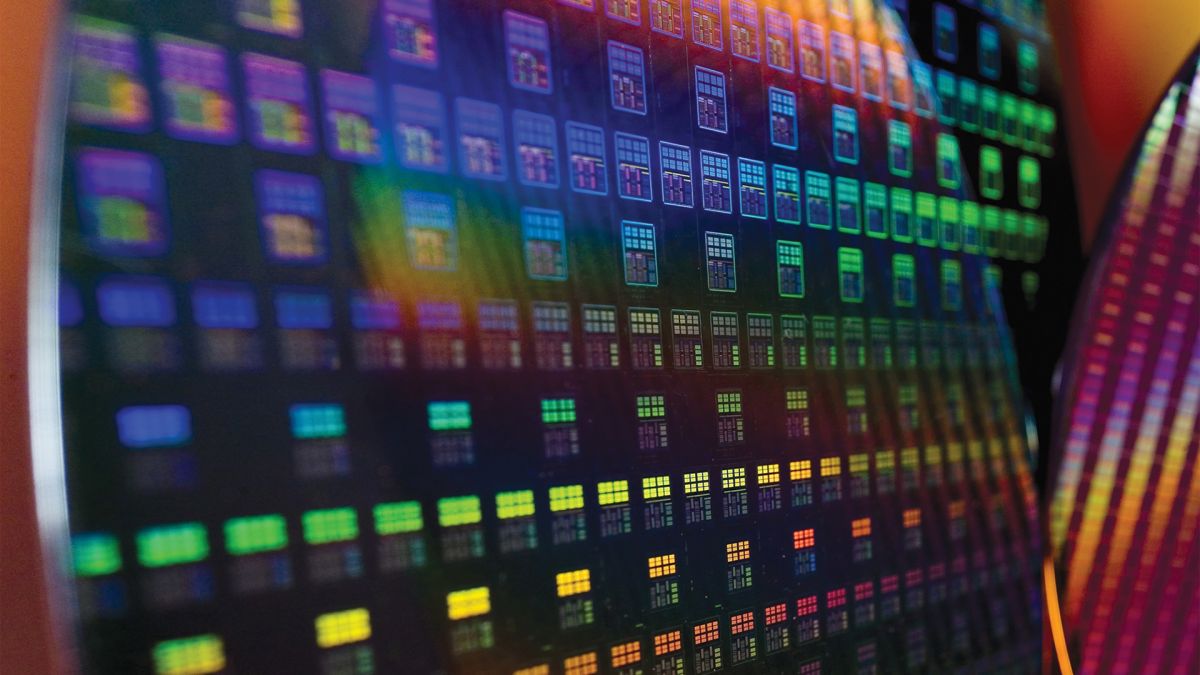

ASML和台积电披露更多有关3 nm制程技术的细节

台积电制造有限公司。台积电(TSMC)是首家使用极紫外(EUV)光刻工具进行大批量生产的公司。到目前为止,该公司已经开发了至少三种使用EUV进行精选层的工艺,并获得了相当多的如何使用新设备的经验。台积电将继续扩大EUV在其下一代技术中的使用,其3 nm(N3)节点预计将在20多层中使用EUV。

目前,台积电有三种使用EUV光刻的制造工艺:N7+、N6和N5。台积电的第二代7 nm技术将EUV用于最多四层,以减少在制造高度复杂的电路时使用多图案化技术。该公司的6 nm工艺是为那些想要重复使用为第一代7 nm设计的IP,但仍想利用EUV略微增加晶体管密度的客户而设计的。那些需要大幅提高晶体管密度和性能(与N7+相比)的客户可以选择台积电的N5节点,它可以使用EUV长达14层。

展望未来,台积电计划向其客户提供N5P和N4制造工艺,这些工艺将主要基于N5技术,并将提供一些性能和功率优势。这两种工艺都将在IP和设计规则层面上与N5兼容,并将为芯片开发商提供轻松的迁移途径。预计N5P将在2021年提供给台积电的客户,而N4将在2022年推出。

台积电的下一代制程技术-N3-将提供比N5更全面的节点改进。特别是,半导体合同商承诺获得高达15%的性能提升(在相同的功率和晶体管数量下),高达30%的功耗降低(在相同的时钟和复杂性下),以及高达70%的逻辑密度提升。根据ASML的说法,N3最有趣的细节之一是,它将在20多个层上使用EUV。

ASML首席执行官彼得·温林克(Peter Wennink)表示:我认为,在N5的逻辑上,我们将超过10层,而在N3,我们将超过20层,我们实际上看到这一数字正在悄悄上升,ASML的首席执行官彼得·温林克(Peter Wennink)表示。事实是,转向单一图案并取消这些多图案DUV策略会带来更多的优势,DRAM也是如此。";;这正是事实,因为它提供了更多的优势,并取消了这些多图案DUV策略,这对DRAM也是如此。

事实证明,台积电对EUV工具和ASML的能力非常有信心,能够提供大批量制造所需的数量,这就是为什么它使其客户能够使用EUV多达20层。

台积电的N3专为移动和高性能计算应用而设计,将使用FinFET晶体管结构,很可能是一个将在未来多年使用的长节点。在N3之后是N2,它将依赖GAAFET(Gate All)结构,并将要求台积电的客户和合作伙伴大幅重新设计他们的芯片和IP。因此,向N2及其后继者的过渡可能需要一些时间。

这些工具在金钱和时间上都很昂贵。它们令人难以置信地复杂和庞大。你必须加固你的人造地板才能承受一个人的重量。您还必须在天花板上安装经洁净室批准的龙门起重机系统,以便在维护期间移动工具的大块。看到这一幕简直是疯了。

回覆。

它使其客户可以使用EUV覆盖多达20多层,那么是多还是少了20层呢?或多或少。

回覆。

它使其客户可以使用EUV覆盖多达20多层,那么是多还是少了20层呢?或多或少。

可能吧。在合理的范围内。

回覆