Skywater-PDF计划在2020年推出第一个130 Nm晶圆

您可能已经看过Maya Posch关于来自Google和Skywater Technology的第一个开源ASIC工具的文章。它设想增加制造定制芯片(专用集成电路)的机会,这些芯片使用开源工具设计,并通过现有的芯片制造设施实现。我的第一个想法是什么?涂胶带要多少钱?也就是说,我如何将屏幕上的设计拿到手中,并将实际的部件拿到手中?我请谷歌的蒂姆·安塞尔(Tim Ansel)更多地解释一下这个项目的目标,以及我将如何获得我的角色。

目标相当直截了当。Tim和他的合作者希望看到硬件以与软件相同的方式开放。团队以彼此的工作为基础的模式,无论是直接协作还是间接协作,都产生了许多功能非常强大的软件。Tim取得了一些成功,让人们对FPGA开发感兴趣,并帮助开发了用于此目的的开放工具。定制ASIC是下一个合乎逻辑的步骤。

当然,FPGA和ASIC并不是解决所有问题的答案。我们不由自主地注意到,您看到的一些例子--包括我们的例子--有时更有利于学习,而不是实际应用。例如,学习FPGA上的状态机的经典示例是红绿灯。为什么不行?每个人都知道它应该做什么,它有清晰的状态逻辑,如果它能感知车辆和人行横道按钮或基于时间表的变化,你可以让它变得尽可能简单,也可以变得相当复杂。

但是,如果您真的在构建一个红绿灯,那么在FPGA中实现就没有多大意义了。即使是最简单的微控制器也能胜任这项任务,而且在购买和工程成本方面都要便宜得多。

ASIC占据着类似的利基市场,但略有不同。从好的方面来说,它们应该比类似的FPGA密度更高、速度更快、耗电量更少。这是有道理的,因为ASIC是一种FPGA,其中的互连是用专用的金属线实现的,而不是通常可配置的。您还可以精确地写下您想要的电路-或者,至少从各种单元中选择,而不必使用FPGA架构师决定您需要的任何东西。您甚至可以在数字电路旁边加入模拟单元。

消极的一面是,ASIC不适合草率的人。从历史上看,生产ASIC一直是非常昂贵的。所以您有一系列的部件,但是-哎呀-您忘记了计数器需要重置为一个非零数。在FPGA中,这是一个很小的麻烦;您只需更改配置-特别是现在在某些应用程序之外,一次性可编程FPGA很少。即使你不得不扔掉一个FPGA,再对另一个进行编程,它们通常也不是很贵,除非它们是防辐射的或非常大的器件。

如果你在ASIC上犯了这样的错误,你就有大麻烦了。你不能对你已有的零件做任何改动。你必须用新的前期成本建造一批新的产品。在商业世界里,这种错误可能会毁了你的职业生涯。

不过,蒂姆明确表示,他的目标受众不是专业的定制ASIC。是我们。想要创建定制IC的黑客和修补工。也可能会有一些学生市场,尽管学校经常有交易来使这一点变得可行。

不过,蒂姆确实指出,许多学校协议都与学生必须签署的保密协议捆绑在一起,因此开放工具可能会刺激新发表的研究,这将是一件好事。尽管如此,我还是感觉到他们认为最感兴趣的将是我们的社区。

值得注意的是,正在使用的130 nm工艺并不是尖端技术。Skywater Technologies工厂由赛普拉斯半导体公司于1991年在明尼苏达州布鲁明顿建造。蒂姆说,专业设计师已经远离了这些大的几何形状,我们的设计师可能不得不重新发现一些沿途丢失的知识,才能最大限度地利用目前在更大工艺上制造的IC。但现有的基础设施是让这个项目变得更负担得起的一大部分。

关于卓越的细胞库,以及每个细胞库是如何针对不同的目的(例如,高密度、低功耗或高速度)进行调整的,Tim有很多话要说。然而,我们想知道怎样才能得到真正的零件。显然,一些细节还在研究中。

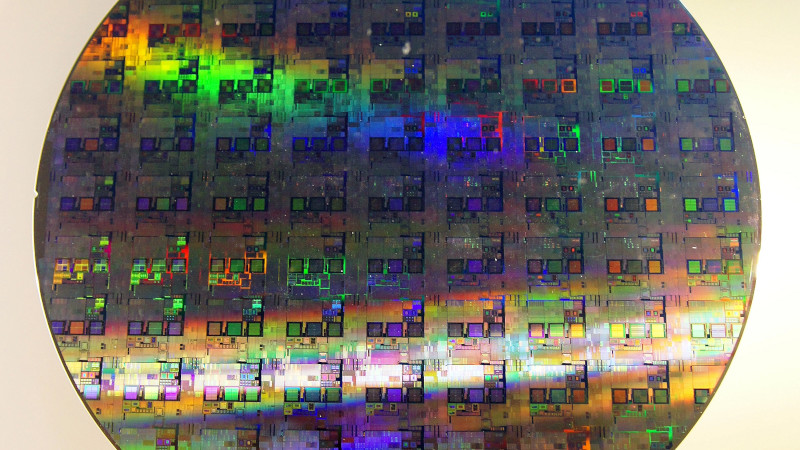

11月份,他们计划订购一款有40个插槽的多项目晶圆。他们还不知道是要苦苦哀求才能拿到40个设计,还是要从所有可能的候选者中筛选出来。如果你是40个人中的一个,你将得到大约10 mm的方块来玩,最终会得到大约100到300个芯片级封装(CSP)的芯片。在随附的照片中,你可以看到一个典型的CSP坐在一美分钱上。

有几个规定。您将在GitHub(或类似的公共存储库)上提交您的设计,因此您的设计将是开源的。这意味着即使你不是这40人中的一员,你也只是把你的芯片拿出来让世界看到了。铸造厂将自动检查您的设计以满足某些技术标准。在这个早期阶段,关于他们将如何选择要包含在第一次运行中的设计,似乎还没有一个明确的计划。想必,如果进入者很多,事情运转良好,2021年会有更多的晶圆。

还有很多问题没有回答。你能付钱把你自己的录像带拿出来吗?如果是这样的话,您还必须是开源的吗?如果你做了一些,然后又想要更多怎么办?那要多少钱?这还为时过早,我们确实还不知道这些问题的答案,但随着时间的推移,细节将会浮出水面。

就像我前面说的,ASIC并不适合每个人,当然也不是为那些边走边测试和调试的人准备的。验证是ASIC项目成功的关键。这意味着这在很大程度上将取决于可用的模拟工具和可用的模型的质量。花费大量的时间和金钱来获得不能以你需要的速度工作、消耗比你预期更多的电力或者根本不能工作的IC是令人心碎的。

很多时候,在尝试使用ASIC之前,可以使用FPGA来验证您的部分或全部设计。当它起作用的时候,它就起作用了。然而,由于这两种技术之间的差异,它并不像将ASIC视为固定的FPGA那么简单。您可能会遇到从手线电路到PCB的相同问题。从逻辑上讲,它们是相同的。但我们都知道,由于不同的特点,你在过渡过程中可能会遇到问题。这里也有同样的问题。您如何测试您的模拟单元?钟表的分布会一样吗?并且ASIC具有在验证阶段难以模仿的速度或功率要求。

蒂姆·安塞尔(Tim Ansel)今天在网上发表了一次演讲,正式宣布了这个项目。查看有关流程节点本身和用于为其设计的工具的更多详细信息:

那么你会试着设计你自己的IC吗?我以前参与过ASIC开发,但我可能仍然有兴趣做我自己的项目,仅仅是为了能够完成所有的步骤。请在评论中让我们知道您想设计什么IC-或者看到其他人设计。