逻辑,先于IC

所以,你需要在合成器中有一个简单的数字逻辑功能。也许它是一个与门,或者几个异或,也许和移位寄存器一样多。你将如何建造它?

今天,仅仅附加一个微控制器芯片通常是有意义的。它们物美价廉,用途广泛。同样的微控制器可以被编程用于多种不同的目的,所以你可以只保留几种类型的库存,大量购买,这样就可以降低成本。如果你需要更高的速度,那么使用FPGA(现场可编程门阵列)可能是有意义的,但很少有合成器电路真正需要这么高的速度。

二三十年前,在微控制器还没有便宜之前,做少量数字逻辑的通常方式是外加几块MSI(中型集成)逻辑芯片,比如基于双极型晶体管的7400或74LS00系列,或基于CMOS的4000系列。这些是小的逻辑构建块,通常每个14针或16针DIP芯片上都有几个门。在这些系列中有几十种流行的芯片和几百种不太常见的芯片。它们最早出现在20世纪60年代末,但直到20世纪70年代中期才性价比高,对业余爱好者来说很容易买到。这样的芯片仍然存在,你仍然可以在DIY设计中看到很多,但随着更便宜的微控制器变得更能吸引大多数市场的大型商业利益,它们正逐渐退出生产。

甚至在过去,任何类型的集成电路都太贵了,不能成为业余爱好者的首选,我们不得不一次用一个有源器件(晶体管甚至电子管)来制造东西。我在我的MSK012晶体管ADSR中使用了这种逻辑。用最少的晶体管建造的逻辑门根本就不是数字的:它们可能更好地理解为碰巧在放大数字信号的模拟放大器电路。随着晶体管变得更便宜,我们今天通常使用的芯片及其内部的栅极已经变得更加复杂,涉及到更多的晶体管,但它们可以被理解为只是从最简单的栅极开始的进化发展。

这里是最简单的逻辑门之一:电阻晶体管逻辑(RTL)反相器。您有时会看到更复杂的电路,通常会增加一个或两个更多的电阻器,以更好地管理电压和电流电平,称为RTL逆变器,但绝对最简单的方法是只使用一个电阻器和一个晶体管。

如果电流流入输入,晶体管将在饱和模式下导通。它以非常低的阻抗将输出拉低--也就是说,拉到晶体管的饱和电压,可能约为0.2V。如果电流没有流入输入端,则晶体管关断,然后电阻器将输出端拉高至电源电压,但阻抗等于电阻值。我已经用27kΩ编写了代码,但实际使用的电阻可能会因应用程序的不同而有所不同。

这是一个相当挑剔的电路,在如何使用它方面有几个陷阱。输入端看起来像一个二极管接地,所以它不可能超过0.6V而不会吸收过多的电流并对晶体管造成损坏。该输出在低状态下具有低阻抗,但在高状态下具有相对高阻抗。高电压不是电源电压;它是根据以下输入的特性浮动到的任何电压。

碰巧RTL输入和输出的特性正是它们相互连接所需要的。在高状态下,输出的高阻抗将允许实际电压降至驱动下一个栅极的输入晶体管所需的电压,而在低状态下,电压被硬拉至足够低的电压以牢固地关闭输入晶体管。你可以或多或少地自由地把像这样的门连接在一起。但是,将简单的RTL门连接到其他设备可能需要更多的电路才能使电压和电流正确。在一种状态下混合高阻抗,在另一种状态下混合低阻抗可能会产生棘手的后果。

让我们看看一个更复杂的门。这里是一个与非门,以类似的最小逻辑方式构建。

单个晶体管已被串联的两个晶体管取代。如果它们都打开,则输出会被拉低。否则,如果至少有一个电源关闭,则不会有电流流过这对电源,因此输出会很高。这提供了双输入与非逻辑功能。

这条赛道有很多注意事项。当施加到Q1的输入为低而另一输入为高时,大部分电源电压在Q1的基极-发射极结上反向施加。晶体管最好能额定那么高的电压。分立晶体管的额定电压通常在该结上约为5V,考虑到还涉及到其他几个降,这意味着5V的电源应该是安全的;但它需要仔细注意所使用的特定晶体管型号。处于低状态的输出电压将是晶体管饱和电压的两倍,这应该足够低,以便在随后的栅极输入中稳定地关断晶体管。但是,如果扩展到两个以上的输入,串联更多的晶体管,这种门的输出电压可能不够低,无法工作。需要考虑这样的事情是使用极简主义门电路所涉及的权衡的一部分,而不是使用额外的元件来提供限制较少的输入和输出特性的更复杂的东西。

当有一个具有一个功能的串联电路时,通常有一个具有互补功能的并联电路,这里就是这种情况。把晶体管并联,而不是串联,它就变成了或非门。

这里,如果一个输入端或两个输入端均为高电平,打开其相应的晶体管,则输出被拉低。否则,当两个输入均为低时,电阻器将输出拉高。该电路可以扩展到比NAND电路问题更少的附加输入,因为晶体管上的电压不会堆叠;在三个或四个晶体管并联的情况下,输出电压仍然可以低至其中一个晶体管的饱和电压。

我们可以从这些较小的块中构建更复杂的逻辑函数。布尔代数可以将任何公式单独重新排列为足够多的NAND门的组合,也可以单独将NOR门重新排列为NOR门的组合。有时也有捷径可用,比如这个双晶体管XNOR门。否则,XNOR将是一个很难综合的逻辑函数,需要几个更简单的门的组合。

由于电路中没有其他电压,因此两个输入端均为高电平,因此输出也必须为高电平。当两个输入都处于低电平时,每个晶体管的基极和发射极电压都很低,它就会关断,输出就会再次变高。在一个输入为高,另一个为低的情况下,一个晶体管看到反向偏置的基极-发射极结(最好根据所涉及的电压进行额定),而另一个晶体管则导通,从而使输出变低。它构成了XNOR函数。对于XOR门,只需在输出上添加一个反相器;这可能更可取,以确保输出特性良好。

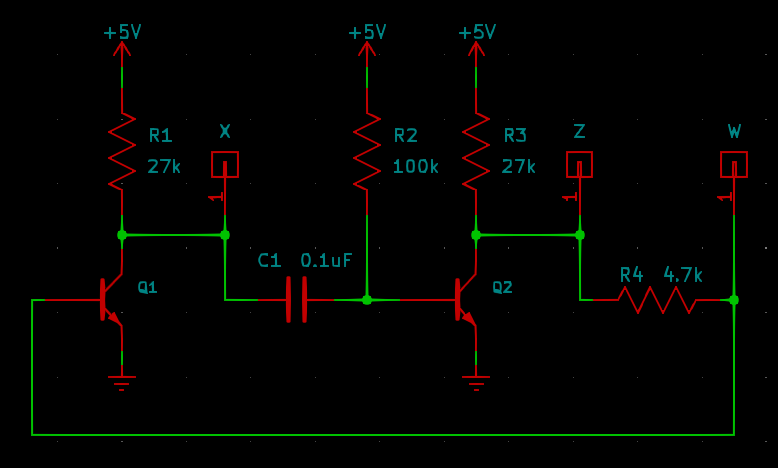

假设我们将两个逆变器连接在一个环路中,输入到输出,中间有小电阻。

如果启用了Q1,则会使标记为X和Y的点都变低。则Q2处于关闭状态,Z和W均为高电平,而Q1保持打开状态。电路在这种状态下是稳定的。另一方面,如果关闭Q1,则X和Y都是高的;Q2将打开,Z和W将是低的,这将使Q1保持关闭状态。这也是一个稳定的状态。

该电路在上电时必然会进入这两种状态之一。哪一个可能是不可预测的,因为它可能由微小的温度差异、噪声尖峰等决定。但是我们可以通过向输入W和Y中的一个施加正电流脉冲来强制它进入特定状态。这就是级之间电阻的原因;输入脉冲需要临时覆盖环路中的前一个晶体管,级间电阻限制了这样做所需的电流量。

这种电路叫做双稳多谐振荡器。它是双稳的,因为它有两个稳定的状态;多谐振荡器将在下面讨论。它是一个存储一位信息的简单数字存储器,在需要在几个不同的不同状态下操作并在它们之间切换的半模拟类型的电路中非常有用。

如果你在网上查找多谐振荡器电路,你会注意到它们通常是以特定的传统布局绘制的,导线在中间呈对角交叉。我在这篇文章中以不同的方式绘制它们,因为我认为保持从左到右的方向可以更容易理解电路是如何运行的。

假设我们不是只在两级之间使用电阻器,而是在一个点上放入RC电路。

如果Q1关闭,R1和R2会将C1的两端以及Q2的底部拉高。然后打开Q2,并通过R4将Q1的底部拉低,使Q1保持关闭状态。电路在这种状态下是稳定的。但是如果我们对W施加电流脉冲会发生什么呢?然后Q1短暂打开。在短时间内(当C1通过R2充电时),电流流过C1,将Q2的基极拉低;这将关闭Q2,允许R3和R4将Q1的基极拉高,并且即使在外部脉冲消失之后也保持Q1打开。但它在这种状态下并不稳定,因为通过C1的电流最终会将其充电到Q2的基极电压上升,Q2接通,电路返回到初始状态的程度。这种电路在一种状态下是稳定的,但在另一种状态下不稳定;它被称为单稳态多谐振荡器,因为它处于一种稳定状态。

单稳态多谐振荡器可以保持其不稳定状态的时间不是由初始电流脉冲决定的,如果我们可以假设它非常短的话。相反,它由C1到R2的充电时间决定。因此,这种电路可以用来产生一个长度可控的脉冲或某种延迟,这就是它经常被使用的方式。

如果Q1打开,则在C1充电的有限时间内,它可以将Q2的基极保持在低电平,从而关闭Q2,并允许Q1的基极保持高电平并保持Q1打开。类似地,如果Q2打开,则在C3充电的有限时间内,它将Q1的基数保持为低,从而使Q2的基数保持高,而Q2的基数保持打开。但这两种状态都不稳定;在每种情况下,电容器最终都会充电到打开下游晶体管的电压,并将电路切换到另一种状态。它一直在来回切换。这个电路是一个不稳定(不稳定)的多谐振荡器。

不稳定多谐振荡器是产生矩形波的振荡器:交替的高和低脉冲,高和低时间的长度分别由对C1和R2以及C3和R4控制。在集成电路面世之前,这种简单的双晶体管振荡器曾经是设计音频振荡器的一种非常常见的方法,用于像Morse code Practice这样的应用。

不稳定多谐振荡器电路最早是在20世纪初开发出来的,当时它们是用管子建造的。当时,由于更复杂的测试设备还没有发明出来,人们经常希望以固定的频率间隔使用标记信号来调谐和测试无线电。如果你从10千赫的方波开始,比如说,它的主次谐波会是它的奇数倍:10千赫,30千赫,50千赫,等等。如果方波有尖锐的角落,它将包含大量的能量,很好地进入兆赫范围。少量的失真也会在甚至多个频率上产生更小的尖峰。如果你有这样一个信号的精确频率源,你可以把它输入你的接收器,并根据它们相对于规则间隔标记的位置来确定其他信号的频率。通过调整多谐振荡器以使其中一个谐波与已知参考值一致来校准多谐振荡器,也将校准其他谐波的频率。

对于这种应用,不稳定多谐振荡器电路比以前的电路更先进,因为它自然会产生方波。当时常见的其他振荡器通常基本上是正弦振荡器,需要进一步放大和修剪才能产生类似方波的输出。所以这个电路的特别之处在于,与正弦振荡器不同的是,它可以很容易地同时产生多个频率的频谱:多个振动,因此是多个振荡器。(亨利·亚伯拉罕(Henri Abraham)和尤金·布洛赫(Eugene Bloch)在最初的论文中对法语术语Multiviateur进行了英语化。)。然后,由于电路被推广到也包括具有一个或两个稳定状态的版本,人们添加了不稳定、单稳定和双稳定三个词来描述基本的双元件开关电路的不同变体。

我已经描述了极简电阻晶体管逻辑中的几个基本逻辑电路。这些电路,或它们的变体,是人们在IC还不常见的日子里用来做简单数字逻辑的东西。尽管集成电路通常是当今做逻辑的最简单和最便宜的方式,但基本的RTL电路展示了芯片中仍在使用的一些原理,它们在某些数字逻辑与模拟电路相结合的设计中仍然适用。我还描述了多谐振荡器电路,它以最少的元件实现我们现在可能使用定时器和触发器IC实现的功能。

我已经很久没有贴过玉米热狗了,所以这里有一些。