Nvidia Ampere与AMD RDNA 2:体系结构之战

对于GPU爱好者来说,这是一个漫长的等待。 Nvidia将Turing产品线维持了两年,然后在2020年9月用Ampere取代了它。AMD有点友善,他们的新设计之间有15个月的差距,但是大多数人对此并不感兴趣。

他们想要看到的是AMD推出了一款高端机型,与Nvidia的顶级机型进行正面竞争。他们就是这样做的,现在我们已经看到了结果,在花钱购买性能最好的显卡时,PC游戏玩家现在被选择(至少在理论上)宠坏了。

但是为它们供电的芯片又如何呢?他们中的一个人从根本上优于另一个人吗? 继续阅读,以了解Ampere和RDNA 2如何与之抗衡!

高端GPU多年来已经比CPU大很多,并且它们的尺寸一直在稳定增长。 AMD的最新产品面积约为520 mm 2,是其先前Navi芯片的两倍多。不过,这并不是他们最大的荣誉,该荣誉是在他们的新型Instinct MI100加速器(约750毫米2)中获得的。

AMD上一次制造接近Navi 21尺寸的游戏处理器的原因是Radeon R9 Fury和Nano卡,它们在斐济芯片中采用GCN 3.0架构。芯片面积为596 mm 2,但它是在TSMC的28HP工艺节点上制造的。

自2018年以来,AMD一直在使用台积电(TSMC)较小的N7工艺,该生产线中最大的芯片是Vega 20(在Radeon VII中发现),面积为331 mm 2.所有Navi GPU均为它是在该过程的稍有更新的版本(称为N7P)上制成的,因此可以比较这些产品。

但是,就绝对尺寸而言,Nvidia夺冠,但这不一定是一件好事。最新的基于Ampere的芯片GA102为628 mm2。实际上,它的尺寸比其前身TU102小约17%,即GPU的芯片面积惊人地达到了754 mm 2。

与Nvidia巨大的GA100芯片(用于AI和A数据中心,该GPU为826 mm 2,是台积电N7芯片。尽管从未设计过为台式机显卡供电,但它确实显示了GPU制造的规模。

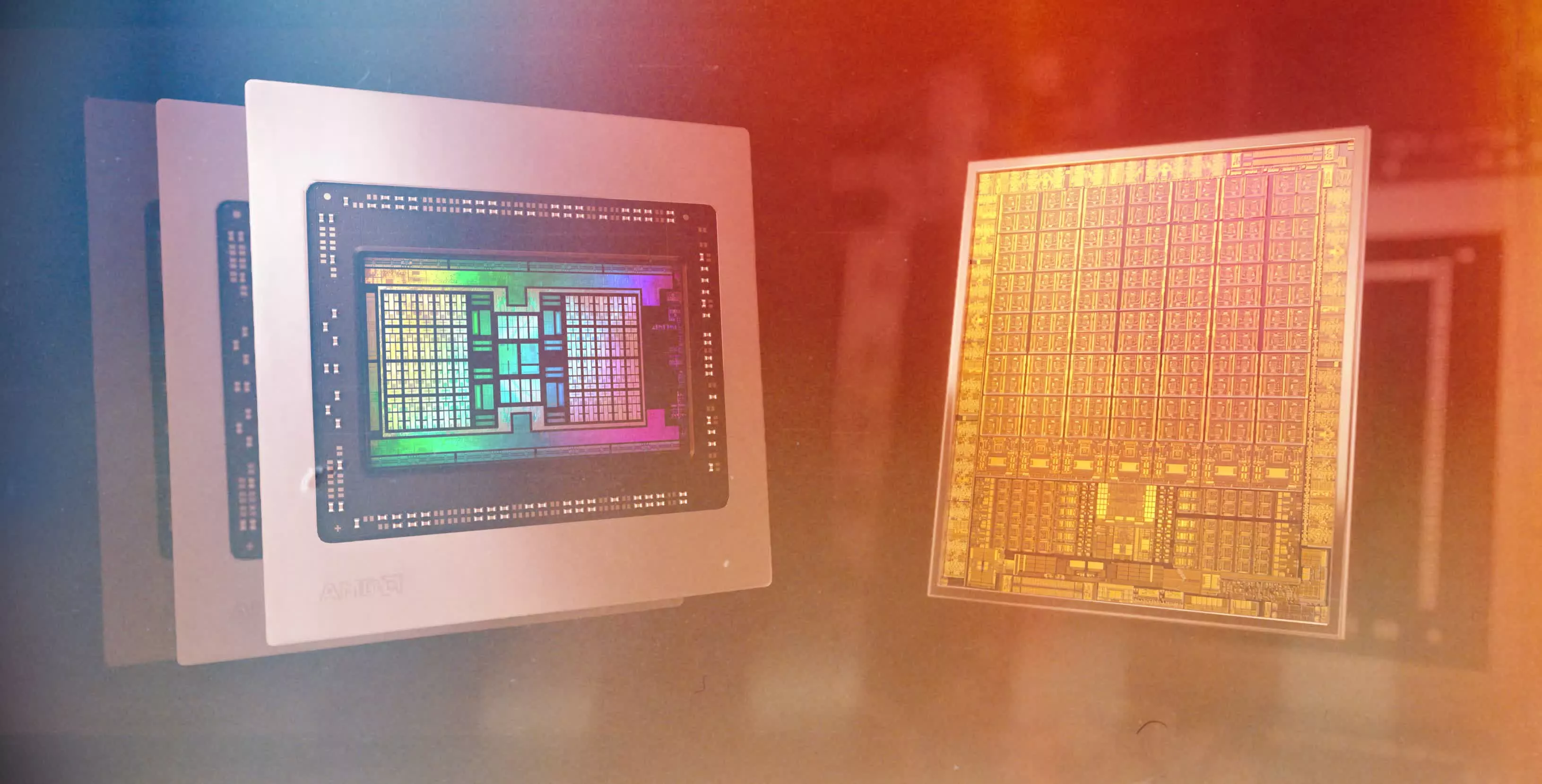

将它们放在一起可以突出显示Nvidia最大的GPU有多庞大。 Navi 21看起来相当苗条,尽管处理器的功能不仅仅是模具面积。 GA102封装了约283亿个晶体管,而AMD的新芯片则少了5%,为268亿个。

我们不知道每个GPU构建多少层,因此我们所能比较的是晶体管与裸片面积的比率,通常称为裸片密度。 Navi 21约为每平方毫米5150万个晶体管,但GA102明显低于41.1,这可能是Nvidia的芯片堆叠度比AMD高一点,但它的更可能是过程节点的指示。

如前所述,Navi 21由台积电使用N7P生产方法制造,与N7相比,性能略有提高。但是对于Nvidia的GA102新产品,他们求助于三星进行生产。这家韩国半导体巨头正在使用经过调整的版本,专门针对Nvidia,即所谓的8 nm节点(标记为8N或8NN)。

这些节点值7和8与芯片组件的实际尺寸没有太大关系:它们只是市场术语,用于区分各种生产技术。也就是说,即使GA102的层数比Navi 21的层数多,裸片尺寸的确会产生特别的影响。

微处理器和其他芯片是由大型圆形圆盘制成的,这些圆盘由高度精炼的硅和其他称为晶圆的材料制成。台积电和三星为AMD和Nvidia使用300毫米晶圆,与更大的芯片相比,使用较小的芯片,每张光盘将产生更多的芯片。

这种差异不可能很大,但是在降低制造成本方面,当每片晶圆的生产成本达到数千美元时,AMD相对于Nvidia而言优势较小。当然,这是假设三星或台积电没有与AMD / Nvidia进行某种财务交易。

如果芯片本身不擅长于设计工作,那么所有这些芯片尺寸和晶体管数的恶作剧将是徒劳的。因此,让我们深入研究每个新GPU的布局,看看它们背后的东西。

我们通过查看Ampere GA102和RDNA 2 Navi 21 GPU的整体结构来开始对体系结构的探索-这些图不一定表明我们在物理上是如何布置的,但是它们给出了明确的指示:处理器有多少个组件。

在这两种情况下,布局都是非常熟悉的,因为它们实质上是其前身的扩展版本。在处理指令中添加更多的单元将始终提高GPU的性能,因为在最新的3D大型电影中,在高分辨率下,渲染工作负载涉及大量的并行计算。

这样的图很有用,但是对于这种特定的分析来说,查看各个组件在GPU自身内部的位置实际上更有趣。在设计大型处理器时,通常需要将共享资源(例如控制器和缓存)放在中央位置,以确保每个组件都具有相同的路径。

接口系统(例如本地内存控制器或视频输出)应放在芯片的边缘,以使它们更容易地连接到成千上万的将GPU与图形卡其余部分连接的独立电线。

以下是AMD Navi 21和Nvidia GA102芯片的伪彩色图像。两者都经过一些图像处理以清理图像,并且实际上都只在芯片中显示了一层。但是它们确实使我们对现代GPU的内在感觉有了极好的了解。

设计之间最明显的区别是Nvidia并未采用集中式的芯片布局方法-所有系统控制器和主缓存位于底部,逻辑单元排成一列。他们过去曾经这样做过,但仅限于中/低端型号。

例如,Pascal GP106(用于GeForce GTX 1060等)实际上是GP104(来自GeForce GTX 1070)的一半。后者是较大的芯片,其缓存和控制器位于中间。这些都移到了它的兄弟姐妹那一边,但这只是因为设计已经被拆分了。

对于所有以前的高端GPU布局,Nvidia使用了经典的集中式组织。那么,为什么要在这里进行更改?可能不是出于接口的原因,因为内存控制器和PCI Express系统都在裸片边缘运行。

这也不是出于热学原因,因为即使芯片的缓存/控制器部分比逻辑部分的温度更高,您仍然希望它的中间有更多的硅以帮助吸收。并散发热量。尽管我们不确定此更改的原因,但我们怀疑这与Nvidia对芯片中的ROP(渲染输出)单元实施的更改有关。

稍后我们将详细介绍这些内容,但现在让我们说的是,尽管布局更改看起来很奇怪,但不会对性能产生重大影响。这是因为3D渲染充满了很多长等待时间,通常是因为必须等待数据。因此,通过使某些逻辑单元比其他逻辑单元更远离缓存,所增加的额外纳秒都隐藏在事物的宏伟方案中。

在继续之前,值得一提的是AMD在Navi 21布局中实施的工程变更,与为Radeon RX 5700 XT之类的处理器提供动力的Navi 10相比。尽管新芯片的面积和晶体管数量都比早期芯片大了一倍,但设计人员还设法在不显着增加功耗的情况下提高了时钟速度。

例如,对于300 W的TDP,Radeon RX 6800 XT的基本时钟和升压时钟分别为1825和2250 MHz。 Radeon RX 5700 XT的相同指标分别是1605 MHz,1905 MHz和225W。Nvidia也提高了Ampere的时钟速度,但是其中一些可以归因于使用更小,更高效的处理节点。

我们对Ampere和RDNA 2卡的每瓦性能检查表明,两家供应商在该领域均取得了显着改善,但AMD和TSMC取得了显着进步-比较Radeon RX 6800和Radeon VII在性能上的区别。上面的图表。

后者是他们首次使用N7节点进行GPU合作,并且在不到两年的时间内,他们将每瓦性能提高了64%。的确,如果英伟达(Nvidia)留在台积电(TSMC)从事生产工作,那安培GA102的性能会好得多。

当涉及到指令处理和数据传输管理时,Ampere和RDNA 2都遵循类似于芯片内部所有事物组织方式的模式。游戏开发人员使用图形API对标题进行编码,以制作所有图像;它可能是Direct3D,OpenGL或Vulkan。这些本质上是软件库,里面装满了' s'规则,结构和简化说明。

AMD和Nvidia为它们的芯片创建的驱动程序本质上可以用作翻译器:将通过API发出的例程转换为GPU可以理解的一系列操作。之后,完全取决于硬件来管理事物,例如首先要完成哪些指令,执行这些指令的芯片的哪一部分等等。

指令管理的初始阶段由合理地集中在芯片中的一组单元处理。在RDNA 2中,图形和计算着色器通过单独的管线进行路由,这些管线将指令调度并调度到芯片的其余部分;前者称为图形命令处理器,后者是异步计算引擎(ACE)。

Nvidia只是用一个名字来描述他们的一组管理单元,即GigaThread引擎,并且在Ampere中它执行与RDNA 2相同的任务,尽管Nvidia并未过多说明其实际管理方式。总之,这些命令处理器的功能类似于工厂的生产经理。

GPU通过并行执行所有操作来获得性能,因此在整个芯片上复制了下一个组织级别。坚持工厂的类比,这类似于拥有中央办公室但在多个地点生产商品的企业。

AMD使用标签Shader Engine(SE),而Nvidia则称其为图形处理集群(GPC)-不同的名称,相同的角色。

对该芯片进行分区的原因很简单:命令处理单元无法处理所有内容,因为它最终会变得太大和太复杂。因此,将一些调度和组织职责进一步推向下游是有意义的。这也意味着每个分离分区都可以做完全独立于其他分区的事情-因此一个分区可以处理大量的图形着色器,而其他分区则可以处理冗长而复杂的计算着色器。

在RDNA 2的情况下,每个SE包含其自己的一组固定功能单元:设计用于执行一个特定任务的电路,通常程序员无法对其进行大量调整。

原始设置单元-准备处理顶点,以及生成更多(镶嵌)并剔除它们

基本设置单元每个时钟周期以1个三角形的速率运行。这听起来似乎不是很多,但是请不要忘记这些芯片的运行频率在1.8至2.2 GHz之间,因此原始设置永远不会成为GPU的瓶颈。对于Ampere,原始单位位于组织的下一层,我们将在短期内进行介绍。

AMD和Nvidia都没有对光栅化器说太多。后者称为Raster Engine,我们知道它们每个时钟周期处理1个三角形,并吐出许多像素,但是没有其他信息,例如其子像素精度。

Navi 21芯片中的每个SE具有4组8 ROP的库,因此总共有128个渲染输出单元。 Nvidia的GA102每个GPC包含2组8 ROP的库,因此全芯片可容纳112个单元。这似乎是AMD的优势所在,因为更多的ROP意味着每个时钟可以处理更多的像素。但是,此类单元需要良好的缓存和本地内存访问权限,我们将在本文后面详细介绍。现在,让我们继续研究如何进一步划分SE / GPC分区。

AMD的着色器引擎被细分为双计算单元(DCU),Navi 21芯片每个SE分配了十个DCU-请注意,在某些文档中,它们也被归类为工作组处理器。 (WGP)。对于Ampere和GA102,它们称为纹理处理群集(TPC),每个GPU包含6个TPC。 Nvidia设计中的每个集群都包含一个称为Polymorph Engine的东西-本质上是Ampere的原始设置单元。

它们也以每个时钟1个三角形的速率运行,尽管Nvidia的GPU的时钟频率低于AMD的GPU,但它们的TPC却比Navi 21的SE多得多。因此,对于相同的时钟速度,GA102应该具有显着的优势,因为完整的芯片可容纳42个原始设置单元,而AMD的新RDNA 2只有4个。但是,由于每个光栅引擎有六个TPC,因此GA102有效拥有7个完整的原始系统,至Navi 21的四个。由于后者的时钟频率比前者高75%,因此在几何处理方面,Nvidia似乎在这一方面遥遥领先(尽管在这一领域没有游戏可能会受到限制)。

芯片的最后一层组织是RDNA 2中的计算单元(CU)和安培中的流式多处理器(SM),这是我们GPU工厂的生产线。

这些是GPU饼图中的主要部分,因为它们包含了用于处理图形,计算以及现在的光线跟踪着色器的所有高度可编程单元。从上图中可以看到,每个芯片仅占整个芯片空间的很小一部分,但它们仍然极其复杂,对芯片的整体性能非常重要。

到目前为止,在两个GPU上如何布置和组织一切方面,还没有任何严肃的交易突破口—命名法都是不同的,但是它们的功能却大体相同。而且由于它们所做的很多事情都受可编程性和灵活性的限制,因此一个人相对于另一个人所具有的任何优势,都只能归结为规模感,即哪个人拥有最大的特色。

但是对于CU和SM,AMD和Nvidia采用不同的方法来处理着色器。在某些领域,它们有很多共同点,但在其他许多领域则并非如此。

由于安培(Ampere)在RDNA 2之前闯入了野外,所以我们首先来看看Nvidia的SM。现在没有必要查看芯片本身的图像,因为它们无法准确告诉我们其中的内容,因此我们使用组织图。这些不应该表示芯片中各种组件的物理排列方式,以及每种类型中存在多少个组件。

图灵对其台式机前身Pascal进行了实质性更改(丢失了一堆FP64单元和寄存器,但是获得了张量核心和光线跟踪),而Ampere实际上是一个相当温和的更新-至少在面值上。不过,就Nvidia的市场部门而言,新设计使每个SM中CUDA内核的数量增加了一倍以上。

在图灵中,流多处理器包含四个分区(有时称为处理块),每个分区中容纳16个INT32和16x FP32逻辑单元。这些电路旨在对32位数据值执行非常具体的数学运算:INT单元处理整数,而FP单元处理浮点数(即十进制)。

英伟达(Nvidia)表示,一个Ampere SM总共有128个CUDA内核,但是严格来说,这不是真的-如果我们必须坚持这一点,那么图灵(Turing)也是如此。该芯片中的INT32单元实际上可以处理浮点值,但只能通过非常少量的简单操作进行。对于Ampere,Nvidia已开放了它们支持的浮点数学运算范围,以匹配其他FP32单元。这意味着每个SM的CUDA内核总数并未真正改变。现在只有其中一半拥有更多功能。

每个SM分区中的所有内核都可以随时处理同一条指令,但是由于INT / FP单元可以独立运行,因此Ampere SM每个周期最多可以处理128x FP32计算或一起处理64x FP32和64x INT32操作。在图灵,只是后者。

因此,新的GPU可能使FP32的输出量比其上一代产品大一倍。对于计算工作负载,尤其是在专业应用程序中,这是向前迈出的一大步。但是对于游戏而言,收益将远远没有达到预期。当我们首次测试GeForce RTX 3080时,这一点很明显,它使用启用了68个SM的GA102芯片。

尽管FP32的峰值吞吐量比GeForce 2080 Ti高出121%,但平均帧速率仅提高了31%。那么,为什么所有这些计算能力都会浪费掉呢?一个简单的答案是,不是,但是游戏并不是一直在运行FP32指令。

当Nvidia在2018年发布Turing时,他们指出,GPU处理的指令平均约有36%涉及INT32例程。这些计算通常用于计算内存地址,两个值之间的比较以及逻辑流/控制。

因此,对于这些操作,双速率FP32功能没有发挥作用,因为具有两个数据路径的单元只能执行整数或浮点运算。而且,只有在当时由它处理的所有32个线程都排队处理相同的FP32操作时,SM分区才会切换到此模式。在所有其他情况下,安培中的分区与图灵中的分区一样运行。

这意味着在INT + FP模式下运行时,GeForce RTX 3080之类的FP32仅比2080 Ti具有11%的FP32优势。这就是为什么在游戏中看到的实际性能提升没有原始数据所预期的那么高的原因。

其他改进?每个SM分区的Tensor Core更少,但每个都比Turing中的功能强大得多。这些电路执行非常具体的计算(例如将两个FP16值相乘并用另一个FP16编号累加答案),每个内核现在每个周期执行32次这些操作。

他们还支持一项称为“细粒度结构化稀疏性”的新功能,并且无需赘述所有内容,从本质上讲,这意味着可以通过删除不影响答案的数据来将数学速率提高一倍。同样,对于使用神经网络和AI的专业人员来说,这是个好消息,但是目前,对于游戏开发人员而言,这还没有显着的好处。

光线跟踪核心也已进行了调整:它们现在可以独立于CUDA核心工作,因此,在进行BVH遍历或射线原始相交数学时,SM的其余部分仍可以处理着色器。 RT Core处理光线是否与图元相交的部分的性能也提高了一倍。

RT核心还具有其他硬件,可帮助将光线跟踪应用于运动模糊,但是此功能目前仅

......