8086处理器如何在内部处理电源和时钟

早期微处理器的一个被低估的特点是难以在集成电路内部分配功率。现代处理器可能有15层金属布线,而20世纪70年代的芯片,如8086,只有一层金属,这使得布线成为一个挑战。同样,时钟信号必须传送到芯片的所有部分,以使其保持同步。

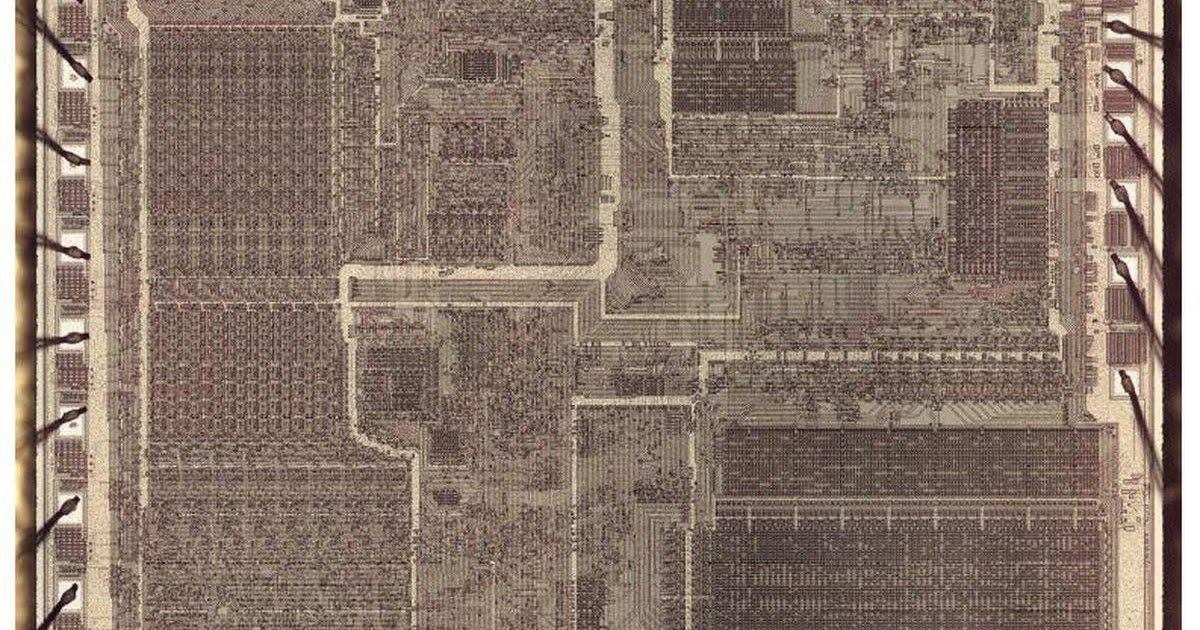

下面的照片显示了8086芯片在显微镜下的情况。芯片顶部的金属层清晰可见,下面隐藏着硅衬底和多晶硅布线。在芯片外部,微小的焊线将芯片上的焊盘连接到外部引脚。8086在顶部有一个电源垫,在顶部和底部有一个接地焊盘。每个电源和接地焊盘都有两根键合线连接,以支持两次电流。您可以从电源和接地焊盘上看到宽阔的金属痕迹;这些焊盘将电源分布在整个芯片上。

8086的模具照片显示电源连接(上)和接地连接(上、下)。时钟电路在底部。

8086的时序由两个内部时钟信号控制。外部振荡器通过底部的时钟输入焊盘向8086提供时钟信号。片内时钟驱动器电路从该外部时钟产生两个高电流时钟信号。请注意,时钟驱动器占据了芯片的一个不重要的部分。

在这篇博客文章中,我将讨论8086如何通过芯片路由电源和时钟信号,以及时钟驱动器电路如何产生所需的时钟脉冲。

8086由三层构成,可用于布线。顶部的金属层最适合布线,因为金属的电阻很低。金属下面是一层由特殊类型的硅制成的多晶硅布线。多晶硅的电阻比金属高,但仍然可以用来在芯片上传输信号。硅衬底是晶体管形成的地方。硅的电阻相对较高,因此它只用于短距离连接,例如栅极内部。

像8086这样的芯片中的电源布线产生了某种拓扑难题:由于金属层的低电阻,金属层是布线电源和地的唯一实用层。必须向芯片中的几乎每个栅极提供电源和地。由于芯片只有一层金属,电源和接地不能交叉。

下图突出显示了8086中的这些金属布线网络。连接到顶部电源引脚的电源以红色显示,贯穿整个芯片。一个主要分支从电源引脚向下向右流动,然后分成多个路径。电源还沿整个芯片的边界传播,提供I/O引脚。

有两个接地针。蓝色的接线连接到上面的接地引脚,而绿色的布线连接到下面的接地引脚。蓝色接地布线在芯片的中心有一个向下的大分支,在复杂的方向上分支。绿色的接地布线沿着芯片的底部、左侧和右侧流动,支撑着I/O引脚,并连接到右下角的微码ROM。

电源线从源到最终目的地变细,因为它们沿途分叉或输送电力,电流减小。这在下面的地址/数据引脚的地线中可见。在左侧,引脚下面的地线非常宽,但向右逐渐变细。换句话说,在左侧,导线必须处理所有引脚的电流,但在右侧,导线只支持剩余的引脚。

与地址/数据管脚的接地连接逐渐变细。(芯片左侧,旋转90°)。

除了电源和地,金属层还用于许多信号;由于其低电阻,它是传输信号的最佳层。然而,广泛的电源和地线限制了金属层的其他用途。为了避免交叉,大多数金属信号线与电力线平行;下面的多晶硅层用于传输垂直信号。但是,如果金属线需要穿过电源线或地线怎么办?解决方案是在电源线或地线下使用交叉,其中。

虽然电源和接地几乎全部在金属层中布线,但也有少数地方发生故障,电源使用交叉引线,这通常发生在线路末端附近,那里的电流很小。下面显示了一个示例,其中地穿过两个多晶硅交叉线。为了减小电阻,这些交叉线比信号交叉线宽得多,并且还同时使用硅层和多晶硅层。小圆圈是金属层和多晶硅层之间的连接(称为通孔)。

硅层在布线电源中只起到很小的作用,特别是许多栅极延伸到电源和两边的接地。下面的照片显示了8086中的一些栅极。请注意延伸到电源线和地线的大掺杂硅区(白色)。这些硅中只有一小部分用于制造晶体管,而其余的看起来像是浪费的空间。然而,这些空的硅区将栅极连接到金属电源和地线上,因为硅的电阻相对较高,所以这些连接使用较宽的区域,而且距离较短。

掺杂硅形成栅可以扩展到电源线和地线。这张照片的金属层被去掉了,所以电源线和接地线都被展示出来了。

当8086被修订并变得更小时,出现了其他的电源布线问题。随着制造技术的改进,英特尔的芯片缩小了,电路保持不变,但统一缩小以生产更小的芯片。不幸的是,缩小电源线会降低它们可以处理的电流。解决方案是加强芯片边缘周围的电源线,同时允许内部电路和布线缩小。这可以在下面的照片中看到;例如,较小的8086的右下角有更多的电源布线。(我在这里写了更多关于8086晶片收缩的内容。)

8086的两个版本在相同的比例下下模。右边的骰子是8086的较新版本,尺寸缩小了。

几乎所有的计算机都使用时钟信号来控制处理器的时序。像许多微处理器一样,8086内部使用两相时钟。5在两相时钟中,有两个时钟信号:当第一个时钟为高时,第二个时钟为低,反之亦然,如下所示。一组电路由第一个时钟启用,而第二组电路由第二个时钟启用。8086的电路要求两个时钟相位不重叠-一个变低后另一个变高后有间隙-并且不对称。6个。

在现代处理器中,时钟布线是复杂的,因为时钟信号必须同时到达芯片的所有部分。现代处理器采用层次结构的时钟路径,平衡每条路径上的时间,并经常为每条路径提供单独的缓冲。相比之下,8086的时钟布线很简单,因为它的5到10 MHz时钟比现代处理器慢几个数量级。在这些相对较低的速度下,路径的长度没有太大区别,所以8086的时钟信号可以在芯片上徘徊。

8086中的时钟路由。绿色是时钟,而红色是相反的相位时钟。

上图显示了8086的时钟路由。相1为绿色,相2为红色。在芯片的底部,产生时钟的电路显示为大水滴。从那里,时钟信号分支缠绕在芯片周围。大部分情况下,两个时钟相彼此平行布线,不像电源和地形成相反的分支。

因为时钟信号到达芯片的所有部分,所以它们需要比典型信号大得多的电流,并且大部分布线在金属层中。当时钟信号必须穿过电源线时,它们使用如下所示的大交叉线。请注意,不规则形状的时钟交叉线比其他信号的交叉线大得多,例如下面的Q总线。

这座钟有很大的交叉线可以穿过电源线。Q总线(其将指令从指令队列传输到解码器)具有小得多的交叉点。

为了提供大电流时钟信号,时钟信号有由大晶体管构成的特殊驱动电路。下图将其中一个驱动晶体管与典型的逻辑晶体管进行了比较。驱动晶体管的大小大约是普通逻辑晶体管的300倍,因此它可以提供大约300倍的电流。该晶体管由10个晶体管并联构成,10条垂直多晶硅线形成10个栅极。每个时钟信号都由一对大晶体管驱动,一个用来拉高信号,另一个用来拉低信号。

下图显示了时钟驱动电路。该电路将外部时钟信号分成两相,使两相互不重叠,并对其进行放大。左边的粉红色正方形是外部提供的时钟的焊盘。信号通过一系列晶体管,右边是用于时钟信号的大型驱动器晶体管。棕色布线是构成栅极的多晶硅。许多晶体管都有之字形栅极,以便在可用空间中容纳更大的晶体管。

芯片上的时钟驱动器电路。金属已经被移除,显露出电路中的大晶体管。时钟输入引脚是左边的紫色正方形。

下面的原理图显示了稍微简化的驱动器电路。三角形表示由两个或三个晶体管构成的高电流驱动器;反相输入(用气泡表示)将输出拉低。在左边,时钟输入引脚有一个小电阻和一个二极管来提供一定的保护(与其他输入引脚一样)。接下来,时钟被分成反相(顶部)和反相(底部)。

附加电路可防止时钟重叠:当一个时钟为高时,它通过反相输入迫使另一侧为低。要了解这是如何工作的,让我们从引脚高的CLK开始,这样CLK输入和时钟就是高的,而CLK输入和时钟就是低的。现在,假设引脚输入的CLK变低,导致CLK输入变低,CLK输入变高。但是,输出时钟可以。由于缓冲器上的负输入,在时钟变低之前不会进入高电平。一旦发生这种情况,CLK输入就会通过较低的驱动器,在两个栅极延迟后将时钟拉高。8这一点在于时钟和时钟不会同时切换;在一个变低之后,在另一个变高之前会有一个延迟。这会产生所需的非重叠时钟信号。

8086使用了一些有趣的供电线路,但现代处理器的运行水平完全不同。虽然8086需要350毫安的电流,但现代处理器可能需要超过100安培。8086使用40个引脚中的3个来供电和接地,而现代英特尔酷睿i5处理器有128个电源引脚和377个接地引脚(总共1151个引脚)。尽管现代芯片中的众多金属层解决了8086的布线问题,但现代芯片有新的复杂情况,如多个电源域。

时钟布线在现代处理器上要困难得多,因为在几千兆赫的速度下,即使是一条超毫米的路径也会影响时钟。为了解决这个问题,现代处理器使用H树或栅格等技术来分配时钟,而不是8086的曲折路径。虽然8086有一个简单的电路来产生两相时钟,但现代处理器经常使用锁相环(PLL)来合成时钟,并使用分散在芯片上的多路电路来产生和控制时钟。虽然8086有一个简单的电路来产生两相时钟,但现代处理器经常使用锁相环(PLL)来合成时钟,并使用分散在芯片上的多条电路来生成和控制时钟。

尽管8086比现代处理器简单得多,但它包含了许多有趣的电路。我计划对更多的8086进行反向工程,所以请在Twitter上关注我的更新,地址是@kensheriff。我还有一个RSS订阅源。

由于标准的NMOS门的下拉网络需要接地,上拉电阻需要电源,所以几乎每个门都必须提供电源和地。但是也有一些例外。8086使用一些动态逻辑门,特别是在ALU中用于速度。这些门被时钟拉高,所以它们不需要直接电源连接。8086还使用一些通过晶体管XOR门,这些门被输入拉低,所以它们不需要直接电源连接。8086还使用一些通过晶体管XOR门,这些门被输入拉低,因此它们不需要直接电源连接。8086使用了一些动态逻辑门,特别是在ALU中用于速度。8086还使用了一些通过晶体管XOR门,这些门被输入端拉低,因此它们不需要直接电源连接。

微码只读存储器形成一个很大的区域,没有电源连接,只有地。这是因为只读存储器中的每一行都被实现为一个非常大的或非门,电源上拉在右边边缘。因此,只读存储器门都有电源和地,尽管它看起来像是只读存储器的弱电源连接。-↩。

集成电路的电源和接地通常位于芯片的相反角落或相反侧,这种布局使得在芯片中构建不相交的电源和接地网络变得更容易。8086的电源和地在对角相对的引脚上稍有不同,但在电源引脚附近有第二个接地引脚,解决方案是电源和地的树形分支网络,这些网络是交错的,像手指一样网状结构,可以到达芯片的所有部分。2-↩。

交叉器用于许多线路交叉,不仅仅是电源,而电源线路是关键因素。通常,金属线路用于一个方向的信号,而多晶硅线路用于垂直方向的信号。(这些方向在芯片的不同部分有所不同,取决于信号的主要方向。)因此,信号大部分可以畅通无阻地传输。即使如此,信号也经常从一层反弹到另一层,以使布线工作。-↩。

虽然几乎所有的计算机都是同步的,并使用时钟运行,但IAS机器体系结构(在20世纪50年代流行)是异步的,没有时钟运行。取而代之的是,每个电路在完成时会向下一个电路发送脉冲,触发下一步。20世纪50年代的许多早期计算机都基于IAS机器体系结构,包括CLONE、ILLIAC、JOHNIAC、MANIAC、SEAC和IBM701。对异步计算的研究仍在继续(链路、链路),但是同步设计。

其中,处理器使用时钟来防止电路中不需要的反馈。例如,考虑一个带有电路的程序计数器,它会递增,并将结果反馈给程序计数器。您不希望新值重复递增。

一种方法是使用边沿敏感电路(触发器),它会在时钟变高的时刻更新程序计数器中的值。其思想是,当第一个时钟为高时,电路的前半部分接收输入并进行其逻辑计算,当第二个时钟为高时,电路的后半部分接收来自第一个时钟的输入并进行任何必要的计算,而前半个电路被阻塞。该思想是,当第一个时钟为高时,电路的前半部分接收输入并进行其逻辑计算,而前半个电路被阻塞,这一点是当第二个时钟为高时,电路的第二半接收来自第一个时钟的输入并进行任何必要的计算,而电路的前半部分被阻塞。其思想是,当第一个时钟为高时,电路的前半部分接收输入并进行其逻辑计算,而电路的前半部分被阻塞。

8086对输入时钟有严格的要求,1/3的时间必须是高的。进入8086的时钟信号通常由8284芯片和石英晶体产生。该芯片将其输入时钟除以3,以产生8086所需的33%的占空比时钟。↩。

因为8086使用了动态逻辑,所以它的最低时钟速度也是2兆赫。如果时钟运行速度低于这个速度,在刷新之前就有电荷泄漏的风险,从而导致故障。最低时钟速度不便于调试,因为你不能减慢或停止时钟。-↩

这是对时钟驱动电路的简单描述,尤其是当一个晶体管拉高信号,而另一个晶体管拉低同一信号时,我不确定会发生什么。准确的模拟将取决于两个晶体管的相对尺寸。“↩