英特尔将在“五年内”批量使用纳米线/纳米带晶体管

今年,在国际VLSI会议上,英特尔的首席技术官Mike Mayberry做了一次全体演讲,今年的主题是“计算的未来”。在演讲中,讨论了许多新的制造技术,包括超越FinFET到栅极全向结构,甚至到2D纳米片结构,最终可能完全离开CMOS。在演讲最后的问答环节中,梅伯里博士表示,他预计纳米线晶体管将在五年内批量生产,为英特尔和其他公司的实现奠定一个非常独特的印记。

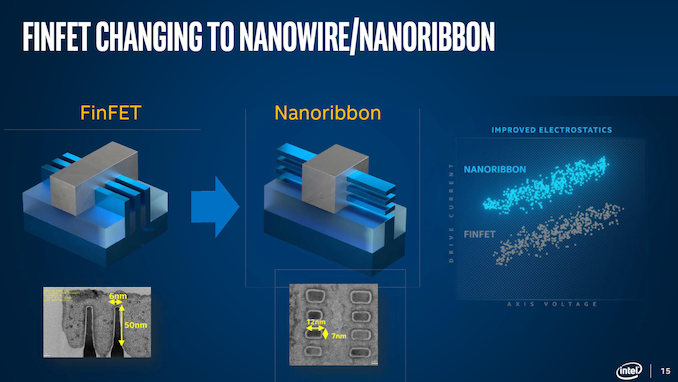

由英特尔在“22 nm”推出的鳍状晶体管,以及其他所有公司在“16 nm”推出的鳍状晶体管,是将驱动电流扩展到平面晶体管之外的一种方式,平面晶体管是实现密度和高性能逻辑的关键指标。英特尔目前正在进行多代FinFET设计,每一代都会增加鳍片的高度,以帮助提升关键指标。然而,就像平面晶体管一样,在自然极限和制造极限之间有一个界限,需要在晶体管设计中进行另一次转变。在这种情况下,已经研发了十多年或需要的Gate-All-All设计。

Gate-All-Around(GAA)设计有许多不同的名称。GAA实现实质上看起来像一个悬停的晶体管鳍片,它可以非常小(纳米线)也可以很宽(纳米片),在驱动电流指标时,多条堆叠线或片增加了晶体管的有效宽度。对于大多数代工企业来说,GAA预计将与“3 nm”节点相交,这应该会提供类似于英特尔“5 nm节点”的密度。

这些GAA晶体管的主要优点之一是,该晶体管可以根据操作要求进行专门定制。具有FinFET的典型晶体管可能需要6-7个离散鳍片的单元高度,因此驱动电流是鳍片计数的函数。采用GAA型设计,不仅实现了堆叠,还实现了片宽,驱动电流现在是一个连续的频谱,这应该可以在硅级别上节省空间和功耗。对于给定的鳍数,FinFET在工艺节点设计中只有一个电源/频率设计点,而GAA允许晶体管设计中的连续比例。

三星已经宣布,它打算在达到“3 nm”工艺节点的阶段将GaA晶体管交付到其制造工艺中。2019年5月,该公司发布了一份新闻稿,作为其Foundry Forum的一部分,称PDK的第一个测试版v0.1已经准备好供其代工客户开始试验。当时,三星预计其3GAE工艺的第一次试运行将于2020年投产,有风险的生产将于2020年底投产,批量生产将于2021年底投产。

在2020年超大规模集成电路技术与电路研讨会期间,英特尔首席技术官兼技术发展总经理Mike Mayberry博士就“计算的未来”做了一次全体演讲。在详细的演示中,Mayberry博士详细介绍了计算如何渗透到各个级别(从设备到边缘再到数据中心),以及对低延迟和高性能的需求如何成为推动这一变化的关键因素。随之而来的是许多设计选项和机会,但也带来了复杂性、成本和计算障碍。推动范式转变的要求之一是制造层面的改变,超越FinFET技术,当我们预计每一家处于领先地位的主要铸造厂都将开始引入GAA技术时。Mayberry博士涵盖了特定领域的架构、内存和电源管理、安全性、系统复杂性、定向自组装、3D晶体管堆叠、异构集成和封装,以及超越标准计算范例甚至CMOS的领域,以此来继续推动计算的极限和计算的无处不在。

有几张幻灯片可能值得在未来的一篇文章中讨论,还有几个问答部分,但梅伯里博士在这个问题上说了一个值得报道的观点。

问:您能告诉我们将纳米带/纳米线工艺技术引入大批量生产的时间表吗?

答:这不是路线图演讲,所以我会含糊其辞,说在未来五年内。

在宣布一项特定技术何时准备就绪时,很难不给出路线图和时间表的暗示,所以尽管梅伯里博士表示他会含糊其辞,但这确实在某种程度上帮助我们缩小了英特尔的一些计划。

值得注意的是,这个问题和梅伯里博士都没有说这是英特尔实施的预测时间表,他本可以更多地谈论英特尔的竞争对手。然而,在这类会谈中,讨论竞争往往在内部引起很大反感,所以这就是为什么我们的印象是,这更多地集中在英特尔生产GAA的能力上,而不是其他任何人。

鉴于我们对英特尔时间表的了解,我们有这张来自英特尔的幻灯片,如2019年9月在SPIE大会上展示的:

对于2021年,英特尔正在准备10++以及一个新的处理节点(7 Nm),我们知道情况就是这样,因为英特尔已经与Argonne的Aurora超级计算机签订了合同,这将是由于英特尔的新Ponte Vecchio HPC加速器内置了部分基于7 nm的加速器。该系统必须在2021年交付,或者至少英特尔必须在2021年达到该系统的一些最低里程碑,所以到那时我们可能会看到7 nm的初步迹象。上面的幻灯片也显示EUV上有7纳米。

假设一切按计划进行,我们有2022年有7+,然后2023年有7++,还有另一个新的工艺节点,据信是5 nm。预计这将是台积电3纳米密度的拐点,这可能表明这是GAA技术可能出现的地方。

再往前看,2024年是5+,2025年是5++和3 nm。如果我是一个赌徒,我预测英特尔在五年内的时间表可能会错过6-12个月的大部分时间,那么2025年可能仍然处于5 nm/5+时代。因此,梅伯里博士说,在5年内实现高产量,明智的投资将是2023-2024年在5纳米处实现GAA。

这是演示文稿的最后一张幻灯片,展示了英特尔对未来15年的展望。量子公司远远超出了英特尔正在做的任何其他事情的范围,梅伯里博士说,在这一点上,它离我们太远了。然而,英特尔正在向深度学习、图形分析和神经形态计算迈进。

发表评论虽然您的最后评论强调,英特尔主要不是QC业务,即您之前提到的低级硬件的日益模拟的本质,由于采用GAA型设计,不仅实现了堆叠,而且还实现了板宽,驱动电流现在是连续的频谱,这也将我们推向必须更好地适应二进制错误概率的设计。为了拓宽我在这篇评论中想要的视角,QC可以被认为是关于设计系统中的噪声,以此作为设计特定算法的更快实现的一种方式。随着噪声的影响在较小规模的电路中变得更加显著,将工程噪声积极用于特定算法,而不是工程噪声,使其对算法没有影响,这一步骤可能是英特尔(以及其他对材料和工艺技术有非常广泛了解的制造商)将能够比目前预期的更顺利地完成的过渡。当然,可能会有很多因素介入,这显然来自于对QM和QC非常具体的观点。回覆。

英特尔最大的问题是销售部门主导市场的心态,这种心态导致拒绝每一次扩张或产能扩张的机会。它们是埃隆·穆斯克的对立面。到目前为止,他们本可以将数十种不同的工艺节点技术投入大批量生产,但他们在5年内只完成了两项。他们本可以建造更多的晶圆厂,并通过更好的摊销来降低成本,但他们却希望控制供应,抬高价格。我不认为他们已经学会了。他们没有远见,没有解决新问题甚至像DRAM这样的老问题的愿望。与埃隆截然相反的是,他想要解决他遇到的每一个问题。老实说,在这一点上,特斯拉更有可能进入像MRAM这样的新领域,而不是英特尔。英特尔正坐在那里,希望找到合适的人,聘用他们,回到领先地位,一切都会稳定下来。事情不是这样运作的。牛顿宇宙并不存在。你要么扩张,要么收缩。回覆。

无精打采的。英特尔扩大了产能,并以与AMD和NVIDIA相同的速度改变了制造流程。如果人们提出的阴谋论一点都不可信,那就太好了。直到英特尔希望控制供应。为什么,面对积压的报告,AMD的晶圆订单会翻一番!回覆。

呃.。典型的英特尔相反命名方案。他们的磁电自旋轨道晶体管是下一个大事件,他们去年的演讲发生了什么?我想答案不是很多。回覆。

有人知道我在哪里可以看到整场演讲吗?或者一切都在收费墙后面?回覆。

英特尔已经在使用可变数量的鳍片/晶体管来调整同一管芯上的晶体管操作(例如,权衡电流容量和漏电),因此这使他们可以更灵活地直接改变栅极宽度,而不是分步改变。回覆。

梅伯里博士表示,他预计纳米线晶体管将在五年内大量生产。当然,我们都期待这一点。问题是,梅伯里博士或其他任何人是否预计英特尔会制造其中任何一种!回覆