对Comtech AHA363 PCIe Gzip加速板进行逆向工程

所有这些工作都是在去年11月完成的。从那以后我就再也没有研究过它,但是其他人已经表现出了兴趣,所以现在是时候把它公之于众了。

同时进行的项目再多也不嫌多。虽然编写RTL很有趣,但我也喜欢逆向工程的整个过程,从一块你一无所知的板子开始,一步一步地走到它变成有用的东西的地步。

Hackaday上的FPGA电路板黑客项目列出了一系列商业上可以买到的带有FPGA的PCB。它们中的大多数并没有真正地进行全面的逆向工程。

支持PCIe的FPGA开发板从来都不便宜,所以我特别喜欢Comtech的AHA363PCIE0301G(AHA363)。如果它能重新用作通用的FPGA PCIe加速板,那就太棒了。

AHA363被列为具有Arria GX FPGA,尺寸未知。它的真正目的是一个gzip压缩和解压缩加速器,这是需要为gzip压缩网页提供服务的数据中心的常见操作。

不同的易趣卖家以非常不同的价格出售相同的电路板:1265美元、185美元和19美元。为了让我的妻子高兴,我选择了19美元的版本。或者更好的是:我买了两个,以防我需要毁掉一个来找出联系等等。

在这篇博客文章中,我描述了从获得董事会到用它做一些有用的事情的过程。不能保证成功:在写这篇文章的时候,我还不能让LED闪烁,但我已经学到了一些新的技术,这些技术将帮助我在未来对其他PCB进行反向工程,这可能对其他人也很有用。

注意:对于那些想要复制/帮助进行反向工程的人来说:现在我们知道了FPGA的类型,真的没有理由再移除散热器了。这降低了意外损坏您的冲浪板的机会。

FPGA Board Hack项目提到了一款Arria GX FPGA,但由于它被散热片覆盖,确切的型号仍不得而知。

散热片牢固地安装在芯片上,两边各有2个夹子。您可以通过在夹孔中插入平头螺丝刀并将其推出来卸下它。稍微摆动一下,安装支架就会脱落。接下来,在FPGA和水槽之间挤压相同的平头螺丝刀,非常轻轻地旋转它,将它们分开。最终,水槽会掉下来,秘密就会揭开:

我们这里有的是Arria GX EP1AGX90E:拥有90K逻辑元件、4.4MB块RAM和176个18x18乘法器的同类最大器件。即使在今天,拥有这种尺寸的FPGA的电路板也在100美元左右。

AHA363的PCB上封装了大量的ASIC和元器件。它是一块半高的4x PCIeboard,带有相同高度的支架:对于机架安装的服务器来说,这很好,但它不适合放在普通PC中。您需要先取下那个支架。

这样做之后,扑通一声(用散热片!)。在我普通的Linux PC上,lspci用以下消息向我打招呼:

我的逆向工程过程的第一步是近距离拍摄所有组件和连接器的照片。在大多数情况下,我的iPhone 7 Plus的x2光学变焦选项就足够了,但有时我会在显微镜上使用iPhone适配器。我的视力一直在下降,照片让我更容易识别各种组件的标记。

我还用组件名称、连接器引脚值等来注释这些照片。这使得在探测事物时需要查找方位时容易得多。

除了一些幻灯片和营销材料,我找不到任何关于它的技术数据表。

基于FPGA的PCIe卡通常使用并行闪存,而不是更常用的串行闪存:并行闪存不仅加载速度更快,而且还支持同一闪存中的多个比特流图像并在它们之间进行选择。英特尔FPGA不支持串行闪存。

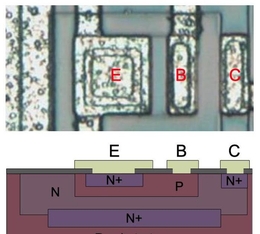

用于将位流从闪存复制到主FPGA中。此CPLD用于Altera Arria GX开发套件中的相同配置,以及远程系统升级设计的参考设计中。

这可能是DC/DC转换器将PCIe供电的12V降至粗略调节的5V,而其他调节器则做更详细的工作。

这块PCB的头部吸引力和它被逆向工程的主要原因!

人们马上就会注意到,这块板在插入PC时会变得相当热,即使它没有做任何有用的事情。

对PCB进行逆向工程最重要的工具是在短检测模式下使用反应时间较短的万用表。这使得可以非常快速地检查过孔阵列,以希望触发2个点之间的连接。

另一个关键因素是首先测量连接的能力:如果您真的很幸运,PCB有很多测试点。如果你运气好的话,有很多通孔没有搭帐篷。如果你没有测试点,通孔是完全没有帐篷的,那你就完全不走运了。在这些情况下,我通常会放弃整个逆向工程:发现联系变得太麻烦了。

Pano Logic G2有主板PCB,没有帐篷通孔。您可以在每个通孔周围看到可接近的空白铜。

但是,Pano Logic G2辅助板有许多可访问的测试点,但其余通孔的铜缆覆盖范围如下:

AHA363板的测试点数量之多令人难以置信,这是我以前从未见过的。所以这真是太棒了。但奇怪的是,我的一块木板上有帐篷通孔,而另一块木板上没有。我用带帐篷孔的那块板用我的示波器记录轨迹,用逻辑分析仪检查动态行为,我用另一块板探测连接。

也就是说,将示波器探头的尖端压在帐篷通孔上通常足以突破保护层,使其稍微脱落。在那之后,就可以毫不费力地探测到这些通孔了。

Arria GX产品家族现在已经相当老了,今天的Quartus版本不再支持它。支持的最后一个官方版本是Quartus 13.0sp1,但那只是标准的商业版本。最后一个“免费”版本是Quartus 11.0。您可以在这里下载。

Quartus Pin Assignment编辑器提供包装IO引脚的出色视图,能够从顶部或底部查看包装,并可任意旋转。当试图在PCB上找到正确的IO焊盘时,这是一个救命稻草。当您将鼠标悬停在其上时,赋值编辑器还会用正确的值注释所有特殊的IO焊盘。

以下是引脚分配编辑器的屏幕截图,显示了从PCB底部看到的Arria GX FPGA,PCIe收发器也位于底部。

当您再次幸运时,PCB在FPGA下面有通孔,直接映射到FPGA封装上的球。

当您的PCB没有此功能时,您可能会被迫在某个时间点将某个电路板的FPGA脱机。

在AHA363的情况下,在FPGA下面有一个相当不错的过孔网格,但要找到过孔和包装上的球之间的相关性仍然有点困难。

是时候拿出一个图像编辑器了(我使用Inkscape,因为它既可以在我实验室的Linux PC上运行,也可以在我的Mac上运行),并开始用最合理的Pad名称注释过孔。这并不总是这里描述的线性过程:我首先定位了一些JTAG引脚(参见下一步),然后注释了这些引脚,然后定位了一些时钟(更往下看),注释了这些引脚等等。

列和行批注位于顶部和左侧。我每5个BGA球加一条网格线。

注意V列和W列之间多了一列球,17行和18行之间多了一排球。这就是我处理过的所有PCB的情况:通孔与BGA上的球不重合,但它们正好落在中间,所以中间总会有一行或一列额外的球。这就是我处理过的所有PCB的情况:通孔与BGA上的球不一致,但它们正好落在中间,所以中间总是有一行或一列额外的球。

在对基于FPGA的PCB进行反向工程时,没有什么比让JTAG接口工作更重要的了,因为它是FPGA开发期间加载位流的主要方法。此外,FPGA还具有适用于大多数IO焊盘的边界扫描寄存器,使得有时可以提取有关如何配置IO(输入或输出)的重要附加信息、定位时钟以及IO正在驱动或正在读取的值。

许多基于FPGA的PCB的JTAG接口很容易获得,甚至在最终的生产板上也是如此,因为它通常用作工厂生产线上的生产固件和位流编程的主接口。

AHA363有一个突出的10针连接器,我预计它会包含JTAGS引脚,所以下一步是找出这些引脚是如何连接的。

10个引脚中有4个接地。它们都在PCB的前面(组件)一侧。

目视检查时,前端的其余引脚似乎未连接(因为没有从连接器金属到任何地方的通孔)。

这样就剩下5个引脚:TCK、TMS、TDI、TDO和VREF。VREF是从PCB到JTAG加密狗中的电压电平移位器的IO电源电压。

发现过程非常简单:从链中所有芯片(TCK或TMS)共享的一个JTAG引脚开始。您可以检查FPGA上的那些IO焊盘和其中一个连接器引脚之间是否有连接。搞定了!

我能很快辨别出TCK和TMS,但对TDI和TDO就没那么幸运了。

问题是TDI和TDO是点对点的,它们可以是链的一部分。如果FPGA处于JTAG链的中间,则FPGA封装上的这些引脚将不会连接到连接器。

因此,下一步是检查CPLD的TDI引脚,答对了:它直接连接到JTAG连接器!

我还确认CPLD的TDO引脚连接到FPGA的TDI引脚。

由于FPGA TDO和连接器之间没有连接,因此这两个ASIC很可能也是JTAG链的一部分。我们对他们的定位一无所知,所以这是个死胡同。

但如果其中一个引脚是VREF,您可以尝试检查两个引脚之一与VDD之间是否有连接。而且,确实是有的!因为现在只剩下未知的了,所以这个可以分配给tdo。

弄清楚JTAG连接器之后,下一步就是让扫描链正常工作。

这显然只有在电路板通电时才有可能,但PCIe卡可以有一个潜在的复杂电源架构:PCIe连接器有12V、3.3V和3.3Vaux引脚,目前还不清楚这块板使用了哪些引脚。

幸运的是,不是在实验室工作台上给电路板供电,还有一种简单得多的方法:把它插到一台正常工作的机器上!幸运的是,我能够从垃圾箱里救出一台非常旧的Mac Pro,除了速度慢之外,它还能正常工作。

我将AHA363 JTAG引脚上的一些电线焊接到采用英特尔USB-Blaster排列的10引脚连接器上,最后得到以下结果:

我启动了Quartus程序员,在按下“Auto Detect”之后,我看到了以下内容:

正如预期的那样,2架AHA363是JTAG链的一部分。这很快就会给我带来大问题…。

在上图中,您可以看到MAX-II CPLD是如何将128Mbit并行闪光灯连接到它的。

我们可能会通过将新的比特流编程到闪存中来摆弄闪存的内容,所以现在是备份它的好时机。

在Quartus Programmer中,选择“CFI_128Mb”旁边的“检查”标志,然后按“开始”按钮。

cfg_128Mb->;右键单击:更改文件(不是添加文件!)->;选择.pof文件->;开始。

当电路板位于PC机箱内时,要对其进行反向工程真的很难!

下一步是在董事会独自坐在长椅上时检测JTAG链。

我们知道电力是通过PCIe连接器进入的,所以我们可以在那里焊接一些电线。但我们也希望仍然能够将电路板插入到工作正常的PC中。

井…。我的零配件包里没有,但我确实有一块又旧又坏的主板!在德雷梅尔行动的几分钟后,我有了这样的感觉:

我很幸运有这样的电源环境:PCIe连接器的3.3V和3.3Vaux引脚不会在PCB上的任何地方,所以整个PCB只由12V供电。

所以我要做的就是在母PCIE连接器上接上12V的针脚。

当对FPGA电路板进行逆向工程时,创建微小的设计来验证引脚输出的假设,然后通过JTAG将该比特流加载到FPGA中是至关重要的。

但请记住JTAG扫描链是如何包含4个器件的:一个MAX-II CPLD、我们感兴趣的Arria GX和2个AHA363芯片。

不管怎样,我无法将SOF文件加载到FPGA中。SOF可以正确切换,但很快FPGA就会收到来自CPLD的重置。我一直在尝试让它工作,但就是不…。

另一种方法是使用所需的位流对FPGA的并行闪存进行重新编程,但要做到这一点,您需要知道该并行闪存的布局。

POF文件包含具有不同类型信息的多个段。如果您知道这些段的内容,您可以自己创建一个新的POF文件并将其加载到FPGA中。

我在网上找到了一份描述POF文件格式的文档!它只有2页,并且提到了最初的Altera Max CPLD设备,所以它可能有20多年的历史了。但总比什么都没有强。

当我在前面从电路板上转储的位流上执行此工具时,我得到了一个包含所有不同块的文件。

=。

有了这些信息,我就能够创建一个.cof文件:Quartus Convert Programming File工具的配置文件,用于将.sof文件转换为.pof文件。

我现在可以闪存一个新的比特流信息并行闪存!大获成功!

不幸的是,这并没有给我带来任何有趣的东西:一旦我加载了一些新的比特流,板子就拒绝工作。我怀疑某些FPGA IO正在控制电路板上的电压调节器,而我的代码显然没有做到这一点。

我只能通过将主板插入Mac Pro,然后刷新原始固件来恢复主板。

还有其他方法可以继续:您可以使用JTAG来转储所有FPGA IO的方向、这些IO所驱动的值或它们正在接收的值。