串扰/SRBDS显示跨CPU核心泄漏信息的可能性

我们首次展示了推测性执行使攻击者能够跨多个Intel CPU的核心泄漏敏感信息,绕过针对先前的推测性(或瞬时)执行攻击(如Spectre、Meltdown等)的所有现有核心内缓解措施。到目前为止,所有攻击都假设攻击者和受害者共享同一核心,因此将相互不信任的代码放置在不同核心上可以阻止此类攻击。相反,我们提出了一个新的瞬时执行漏洞,Intel将其称为“特殊寄存器缓冲区数据采样”或SRBDS(CVE-2020-0543),可使在一个CPU内核上执行的攻击者控制的代码泄漏在另一个内核上执行的受害者软件的敏感数据。

为了发现新的漏洞,我们构建了串扰,这是一个分析器,用于检查复杂(“微编码”)x86指令在CPU内核边界之外的行为。通过串扰,我们发现各种指令执行核外请求,以便从所有CPU核心之间共享的分段缓冲区读取数据。我们观察到分段缓冲区包含敏感数据,包括硬件数字随机数生成器(DRNG)的输出,并且此类数据可以使用RIDL(又名MDS)攻击跨内核泄漏。我们展示了在实践中可以针对在英特尔软件保护扩展(SGX)安全飞地中运行的受害应用程序利用此漏洞进行攻击。具体地说,我们的端到端攻击可能会在仅执行一次数字签名操作之后泄露在单独CPU核心上运行的安全飞地的整个私钥。

我们的相声论文(PDF)被接受在2021年IEEE安全与隐私研讨会上发表。

在过去的几年中,Meltdown、Spectre、Prehadow和RIDL等攻击表明,信息泄漏可能跨越许多现代CPU支持的所有安全域。这是由于现代CPU管道执行的推测性/无序执行,允许攻击者观察内部CPU核心组件上瞬时执行的代码的副作用,如图2所示,例如行填充缓冲区、加载端口、存储缓冲区等。这些微体系结构组件都在同一CPU核心上运行的硬件线程(或超线程)之间共享。如下所示,串扰强制将来自其他内核的信息传输到核上资源,如行填充缓冲区(LFBs),然后使用RIDL检查LFBs的内容。

因此,现有攻击要求攻击者和受害者共享相同的CPU核心,以便利用核上共享的内部资源,并能够在相同或不同的每核硬件线程内泄露受害者的秘密数据。这一限制巩固了这样一种信念,即将不同的安全域(在空间或时间上)隔离在各自的核心上可以防止所有这些攻击。现有的各种减刑措施都明确地建立在这一假设的基础上。

例如,为了应对最近的RIDL攻击,一种选择是禁用同步多线程(SMT)-每个CPU核心只允许一个硬件线程-并刷新同一硬件线程内安全域交换机的微体系结构缓冲区。禁用SMT的另一种成本较低的替代方案是部署安全调度策略,该策略仅允许每个CPU核心有一个安全域。不幸的是,尽管代价已经很高,但这些缓解措施并不能阻止跨核心的瞬时执行攻击。在串扰的情况下,我们证明了这样的攻击是可能的,因此攻击面比先前假设的要大。

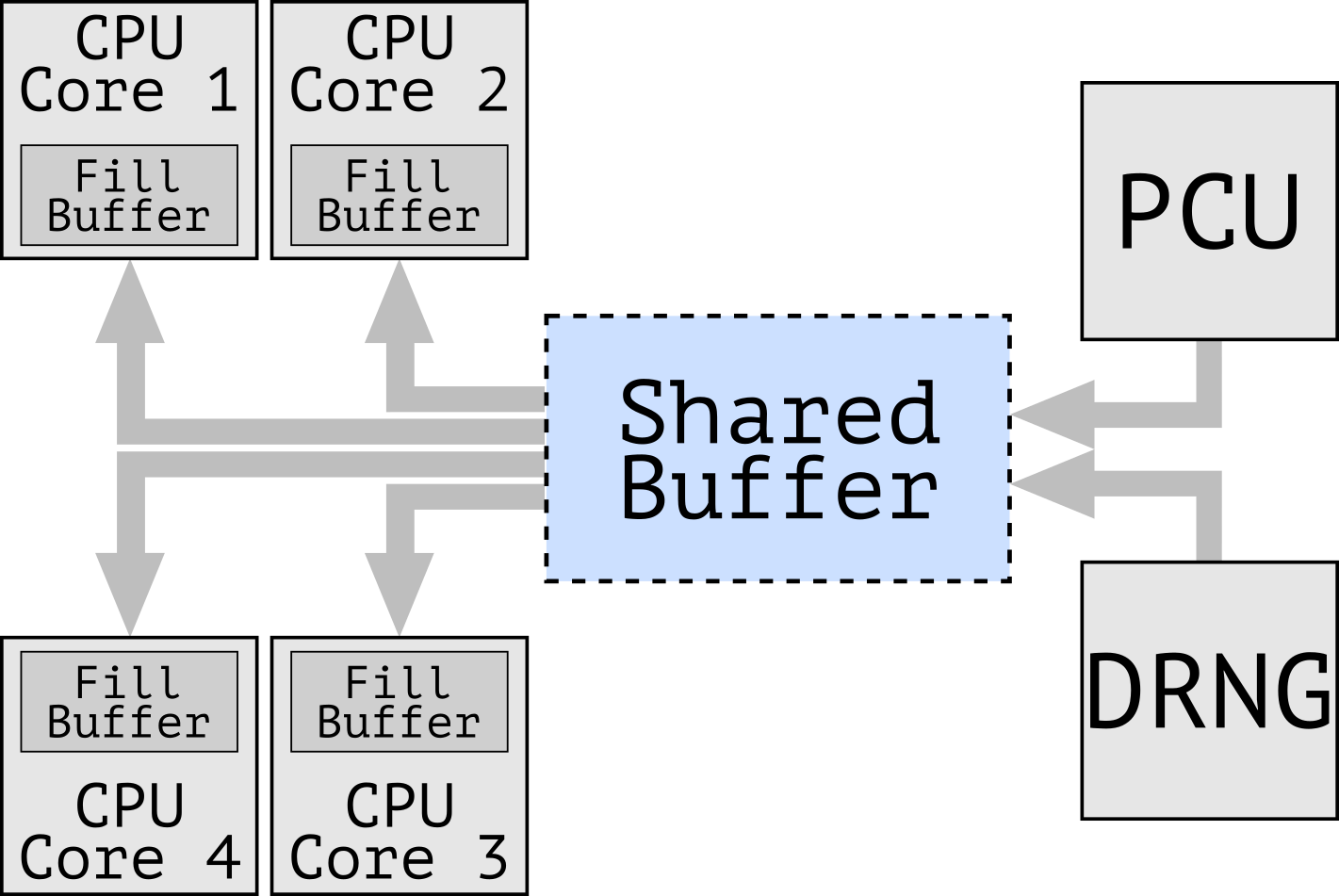

跨核瞬时执行攻击由执行对共享缓冲区的核外访问的指令启用。特别地,如图1所示,我们发现了各种复杂的微编码指令,它们执行对跨所有CPU核心共享的微体系结构缓冲区(我们称为分段缓冲区)的核外访问。有趣的是,分段缓冲区保留所有CPU核心之前执行的核外指令的结果。例如,它包含核心外硬件DRNG(图3)返回的随机数、BootGuard状态散列和其他敏感数据。通过串扰,我们发现在瞬时执行期间从该分段缓冲区读取数据可能会泄漏以前执行的受害者指令访问的敏感数据。

为了研究这种行为,我们构建了串扰,这是一个分析器,用于检查CPU内核边界之外的所有x86指令的行为。串扰(图4)描述了发出核外存储器请求的所有x86指令-生成具有不同上下文(例如,提供不同操作数)的指令。我们使用指令生成阶段的输出结合现有的RIDL攻击来理解核上行填充缓冲区(LFBs)与全局分段缓冲区之间的交互。基本上,我们使用RIDL检查LFBs中的内容

由于不同的指令写入分段缓冲区中的不同偏移量,因此攻击者可以手工创建指令,从而泄露他们想要的所有信息。特别地,串扰的指令剖析阶段使用指令写入分级缓冲器内的不同偏移量的事实来自动发现指令之间的信息如何泄漏。作为输出,它会产生大量指令,这些指令可能会泄漏整个分段缓冲区,包括从系统中不同内核上执行的其他指令请求的任何核外信息。

串扰指令剖析级的设计(图5)如下所示。首先,在一个CPU核心上,我们运行可能与分段缓冲区交互的目标指令。然后,在另一个CPU核上,我们尝试观察分段缓冲区的内容是否因目标指令的执行而改变。为了确保我们观察到分段缓冲区的内容,我们需要确保连续地从分段缓冲区拉取数据。为此,我们使用所谓的分段缓冲区泄漏原语(例如,CPUID 0x80000002)。

为了剖析目标指令(图6),串扰控制的CPU核心首先通过执行泄漏原语来启动分级缓冲器,泄漏原语将控制的数据写入缓冲器内的已知偏移量。并行地,在另一个核上,我们执行目标指令。最后,我们通过与控制数据进行比较来观察任何被覆盖的字节。

我们的分析器帮助我们找到了许多易受攻击指令的分段缓冲区泄漏(表1)。其中,RDRAND和RDSEED特别(安全)重要,因为它们的输出包括由内核外硬件DRNG返回的随机数。

英特尔软件保护扩展(SGX)是2015年随英特尔Skylake微体系结构推出的硬件扩展。SGX提供了一组指令,允许非特权用户程序创建和管理称为安全飞地的加密内存区域,从而保护敏感数据(如加密密钥)不受潜在危害的操作系统和虚拟机管理程序的影响。

为了演示我们发现的漏洞的安全影响,我们实现了第一个跨CPU核心的瞬时执行攻击。我们的攻击可能会泄漏分段缓冲区中的RDRAND和RDSEED指令的输出,这些指令加在一起是CPU为任何英特尔SGX安全飞地提供的唯一可用随机性来源。事实上,我们展示的是,使用此功能,攻击者只需执行一次签名操作即可泄露在单独CPU内核上运行的Intel SGX Enclave的整个ECDSA私钥。

英特尔已在2020年6月9日星期二或更早分发给软件供应商的微码更新中实施了对SRBDS漏洞的缓解。缓解在更新分段缓冲器之前锁定整个存储器总线,并且仅在清除其内容之后才解锁。此策略可确保信息不会暴露给从其他CPU核心发出的核外请求。由于锁定整个系统的内存总线会带来相当大的性能开销,英特尔仅应用了缓解措施来强化少量安全关键指令,特别是RDRAND、RDSEED和EGETKEY(ENCLU指令的叶子)。这意味着发出核外请求的任何其他指令(例如,RDMSR)的输出仍可能跨CPU核心泄漏。

我们在2018年9月披露了显示Staging Buffer内容泄漏的初始PoC(概念验证),随后在2019年7月披露了实施跨核RDRAND/RDSEED泄漏的PoC。在我们的报告之后,英特尔承认了这些漏洞,用英特尔Bug Bounty(侧通道)计划奖励了串扰,并将泄露归因于我们的团队,没有其他独立的搜索者。英特尔还请求禁运至2020年5月(后来延长),原因是难以对本文中确定的跨核心漏洞实施修复。英特尔将我们的攻击描述为“特殊寄存器缓冲区数据采样”或SRBDS(CVE-2020-0543),并将其归类为绕过域的瞬时执行攻击。

我是否可能受到该漏洞的影响?如果您使用的是Intel CPU,则很可能会出现这种情况。英特尔的高端服务器CPU似乎不容易受到攻击,一些最新的英特尔CPU也不容易受到MDS/TAA的攻击。您可以在上面的表2中找到我们测试的英特尔CPU列表。

我如何减轻该漏洞?我们建议安装英特尔的最新微码,其中包括针对RNG输出和SGX密钥的SRBDS缓解功能。这通常是通过标准软件更新机制分发的。

这真的是一个“新”漏洞吗?严格地说,用CVE的话说,是的。同时,潜在问题源于最初的RIDL(又名MDS)类漏洞,但泄漏来源现在是以前未记录的(暂存)缓冲区。由于缓冲区是跨CPU核心共享的,因此该漏洞首次启用跨核瞬时执行攻击。

如果禁用SMT(超线程),我是否会受到影响?是。我们的跨核心攻击不依赖于SMT。事实上,正如您在表2中看到的,我们的攻击是在完全不支持SMT的Intel Xeon E3-1220V6(Kaby Lake)CPU上运行的。

如果我不在英特尔SGX中运行应用程序,是否会受到影响?从理论上讲,是的。该潜在漏洞会导致任意应用程序之间的某些数据(如RNG输出)跨核心泄漏。但是,Intel SGX Enclaves更容易受到实际攻击,因为攻击者可以很容易地减慢受害者的执行速度并控制泄漏。我们预计,在英特尔SGX领域之外的实际利用会更加困难,但并非不可能。

我可以用这个徽标吗?该徽标是免费使用的,通过…放弃权利。。啊,不,等等,我们没有标识,但是如果你真的坚持要在这里买的话。

长达21个月的禁运是怎么回事?我们不会对长时间的禁运掉以轻心,因为我们认为短的漏洞披露期(理想情况下是90天)是给供应商足够的时间来缓解漏洞和及早通知公众之间的一个很好的平衡。我们最初的报告(2018年9月)仅描述了同核(CPUID)泄漏,直到2019年7月,我们才与英特尔进一步讨论此PoC,当时我们报告称,我们为包括RDRAND在内的多个指令复制了跨核泄漏。到那时为止,我们还没有彻底调查这次攻击的影响(显然,英特尔也没有)。我们认识到修复这样的漏洞的复杂性,但正如我们过去明确表示的那样,英特尔应该从一开始就正确修复MDS漏洞-并处理我们报告的POC-而不是玩弄其症状。